# гусс святослав владимирович МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ

ВВЕДЕНИЕ В ДИСЦИПЛИНУ

УЧЕБНО-МЕТОДИЧЕСКОЕ ПОСОБИЕ

# С.В. ГУСС МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ ВВЕДЕНИЕ В ДИСЦИПЛИНУ

Учебно-методическое пособие для студентов, обучающихся по специальностям «Вычислительные машины, комплексы, системы и сети», «Информатика и вычислительная техника».

УДК 004.318

Гусс С.В. Микропроцессорные системы. Введение в дисциплину.

В учебном пособии представлен теоретический материал ПО курсу «Микропроцессорные обучающихся студентов, системы» ДЛЯ ПО специальностям 230101.65 «Вычислительные машины, комплексы, системы и сети», 230100.62 «Информатика и вычислительная техника».

# СОДЕРЖАНИЕ

| ТЕМА 1. ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ |                                                  | СРОПРОЦЕССОРНОЙ ТЕХНИКИ8 |  |

|------------------------------------------|--------------------------------------------------|--------------------------|--|

| Лек                                      | ция 1                                            | 8                        |  |

| 1.1.                                     | Термины и определения                            | 8                        |  |

|                                          | Ключевые определения                             | 8                        |  |

|                                          | Электронные цифровые системы                     | 10                       |  |

|                                          | Особенности традиционных цифровых систем         | 12                       |  |

| 1.2.                                     | Микропроцессор и микропроцессорные системы       | 12                       |  |

|                                          | Микропроцессор                                   | 12                       |  |

|                                          | Управление работой микропроцессора               | 13                       |  |

|                                          | Структура микропроцессора                        | 14                       |  |

|                                          | Требования к разработчику систем                 | 15                       |  |

| Воп                                      | росы                                             | 15                       |  |

| Лек                                      | ция 2                                            | 17                       |  |

| 1.3.                                     | Коммуникация элементов микропроцессорной системы | 17                       |  |

|                                          | Классическая структура связей                    | 17                       |  |

|                                          | Шинная структура связей                          | 17                       |  |

|                                          | Структура микропроцессорной системы              | 18                       |  |

|                                          | Обмен информацией                                | 19                       |  |

|                                          | Виды обмена информацией                          | 20                       |  |

| 1.4.                                     | Разновидности микропроцессорных систем           | 21                       |  |

|                                          | Архитектура с общей шиной для команд и данных    | 21                       |  |

|                                          | Архитектура с раздельными шинами команд и данных | 22                       |  |

|                                          | Типы микропроцессорных систем                    | 22                       |  |

| Воп                                      | росы                                             | 24                       |  |

| TEN                                      | ИА 2. ЦИКЛЫ ОБМЕНА ИНФОРМАЦИЕЙ                   | 25                       |  |

| Лек                                      | ция 3                                            | 25                       |  |

| 2.1.                                     | Пиклы обмена информацией                         | 25                       |  |

|      | Циклы обмена                                           | 25 |

|------|--------------------------------------------------------|----|

|      | Шины магистрали                                        | 26 |

|      | Обмен данными                                          | 27 |

| 2.2. | Циклы программного обмена                              | 28 |

|      | Обмен по мультиплексированной асинхронной магистрали   | 28 |

|      | Обмен по синхронной не мультиплексированной магистрали | 31 |

| Воп  | росы                                                   | 33 |

| Лек  | ция 4                                                  | 34 |

| 2.3. | Циклы обмена по прерываниям                            | 34 |

|      | Типы прерываний                                        | 34 |

|      | Обмен по векторным прерываниям                         | 34 |

|      | Обмен по радиальным прерываниям                        | 36 |

| 2.4. | Циклы обмена в режиме прямого доступа к памяти         | 36 |

|      | Обмен в режиме прямого доступа к памяти                | 36 |

| Воп  | росы                                                   | 39 |

| Про  | межуточный контроль                                    | 39 |

| TEN  | ИА 3. ФУНКЦИИ УСТРОЙСТВ МАГИСТРАЛИ                     | 40 |

| Лек  | ция 5                                                  | 40 |

| 3.1. | Устройство процессора                                  | 40 |

|      | Процессор                                              | 40 |

|      | Схема управления выборкой команд                       | 41 |

|      | Арифметико-логическое устройство                       | 41 |

|      | Регистры                                               | 41 |

|      | Управление                                             | 42 |

| 3.2. | Память                                                 | 43 |

|      | Устройство памяти                                      | 43 |

| Rom  | nocii                                                  | 18 |

| TEN  | ма 4. адресация операндов и регистры процессора  | 49 |

|------|--------------------------------------------------|----|

| Лек  | ция 6 (часть 1)                                  | 49 |

| 4.1. | Адресация операндов                              | 49 |

|      | Адресация                                        | 49 |

|      | Методы адресации                                 | 50 |

| 4.2. | Сегментирование памяти                           | 51 |

|      | Сегментирование в Intel 8086                     | 51 |

|      | Метод сегментирования в Intel 80286              | 53 |

|      | Адресация памяти и сегментирование в Intel 80386 | 53 |

| 4.3. | Регистры процессора                              | 54 |

|      | Регистры процессора Intel 8086                   | 54 |

| Воп  | росы                                             | 55 |

| TEN  | <b>ИА 5. СИСТЕМА КОМАНД ПРОЦЕССОРА</b>           | 56 |

| Лек  | ция 6 (часть 2)                                  | 56 |

| 5.1. | Команды процессора                               | 56 |

|      | Команды пересылки данных                         | 56 |

|      | Арифметические команды                           | 56 |

|      | Логические команды                               | 57 |

|      | Команды переходов                                | 57 |

| Воп  | росы                                             | 58 |

| TEN  | <b>МА 6. ОРГАНИЗАЦИЯ МИКРОКОНТРОЛЛЕРОВ</b>       | 59 |

| Лек  | ция 7                                            | 59 |

| 6.1. | Устройство микроконтроллера                      | 59 |

|      | Классы микроконтроллеров                         | 59 |

|      | Модульная организация микроконтроллера           | 59 |

| 6.2. | Система команд микроконтроллера                  | 61 |

|      | Система команд                                   | 61 |

|      | Память программ                                  | 62 |

|      | Память данных                                        | 62 |

|------|------------------------------------------------------|----|

| 6.3. | Дополнительные вопросы организации микроконтроллеров | 63 |

|      | Регистры микроконтроллера                            | 63 |

|      | Стек микроконтроллера                                | 63 |

|      | Внешняя память                                       | 63 |

|      | Порты ввода/вывода                                   | 64 |

|      | Модуль прерываний микроконтроллера                   | 65 |

|      | Режимы работы микроконтроллера                       | 65 |

| Вопј | росы                                                 | 65 |

| Лек  | ция 8                                                | 67 |

| Про  | межуточный контроль                                  | 67 |

| TEM  | ИА 7. ПРОЕКТИРОВАНИЕ УСТРОЙСТВ                       | 69 |

| Лек  | ция 9                                                | 69 |

| 7.1. | Задачи проектирования микропроцессорной системы      | 70 |

|      | Технико-экономический анализ и обоснование           | 70 |

|      | Использование микропроцессорной техники              | 70 |

| 7.2. | Классификация микропроцессорных устройств            | 72 |

| Вопј | росы                                                 | 76 |

| Лек  | ция 10                                               | 77 |

| 7.3. | Этапы разработки и модернизации                      | 77 |

|      | Системный анализ                                     | 77 |

|      | Выбор типов используемых средств                     | 80 |

| Вопј | росы                                                 | 85 |

| Лек  | ция 11                                               | 85 |

|      | Разработка аппаратных средств                        | 89 |

|      | Разработка программного обеспечения                  | 89 |

|      | Совместная отладка                                   | 92 |

| Воп  | росы                                                 | 92 |

| вопросы для проверки по дисциплине | 93 |

|------------------------------------|----|

| СПИСОК ЛИТЕРАТУРЫ                  | 96 |

# ТЕМА 1. ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ

## Лекция 1

## 1.1. Термины и определения

#### Ключевые определения

Определение 1. Электронная система (в рамках изучаемой дисциплины «Микропроцессорные системы») — система, производящая обработку информации. Такая система может быть представлена электронным узлом (как часть устройства), блоком (в виде совокупности взаимосвязанных элементов и узлов устройства, выполняющих определённую функцию), прибором (как самостоятельное устройство) или комплексом (как совокупность устройств, образующих единое целое).

<u>Определение 2</u>. *Задача* — требование к электронной системе в виде набора функций (внешняя сторона); основная единица работы системы, требующая выделения ресурсов (внутренняя сторона).

<u>Определение</u> 3. **Быстродействие** — показатель скорости выполнения электронной системой своей задачи (внешняя сторона); количество элементарных операций (сложение, сдвиг, ...), выполняемых в единицу времени (внутренняя сторона).

*Номинальное быстродействие* – предельное быстродействие, соответствующее определённому режиму использования устройства.

<u>Определение 4</u>. *Гибкость* – способность электронной системы подстраиваться под определённые задачи (в этом случае говорят об эксплуатационной гибкости).

В традиционном понимании, гибкость системы – свойство системы, состоящее в возможности её совершенствования, расширения и придания ей новых качеств.

<u>Определение 5</u>. *Избыточность* — степень соответствия возможностей электронной системы решаемой задаче. Когда говорят об избыточности, подразумевают дополнительные средства (программные или аппаратные), вводимые в систему для повышения её надежности и защищённости.

*Алгоритмическая избыточность* – дополнительные средства, включенные в алгоритм решения задачи, удаление которых не влияет на результат. Такая избыточность используется для повышения достоверности результатов.

Функциональная избыточность — дополнительные функции и компоненты системы, наличие которых не является принципиально необходимым для реализации возлагаемых на неё задач.

Предположим, что у нас есть электронная система, которая способна предоставить определённый функционал своему пользователю (табл. 1.1). Назовём функции системы – возможностями (№1, №2, №3).

Пусть возможность №1 будет реализована с низким уровнем качества, возможность №2 будет реализована с высоким уровнем качества, а возможность №3 со средним уровнем качества. Также допустим, что нашей системе необходимо решать задачи, в которых требуется, чтобы все возможности системы были реализованы со средним уровнем качества. В таком случае, наша система не будет обладать достаточным уровнем избыточности, поскольку одна из возможностей реализована на низком уровне. С другой стороны, если задача требует низкого уровня реализации возможностей системы, тогда наша система будет избыточной и в случае необходимости она будет способна выполнять задачи, требующие высокого уровня качества возможности №2 или, например, среднего уровня возможности №3.

Таблица 1.1 Избыточность электронной системы (иллюстрация к примеру)

| Уровень качества | Низкий | Средний | Высокий |

|------------------|--------|---------|---------|

| Функции          |        |         |         |

| Возможность №1   | +      |         |         |

| Возможность №2   |        |         | +       |

| Возможность №3   |        | +       |         |

<u>Определение 6</u>. *Интерфейс* – правила обмена информацией между устройствами, участвующими в обмене.

Внешний интерфейс — средства и правила взаимодействия подсистемы с внешними объектами (пользователем, вычислительной сетью).

*Внутренний интерфейс* – интерфейс с внутренним компонентом системы (или между внутренними компонентами системы).

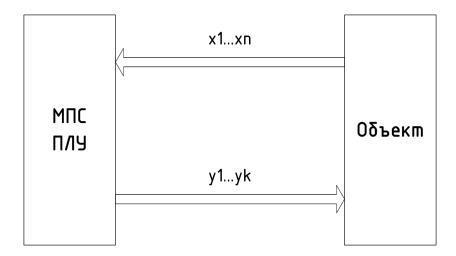

<u>Определение 7</u>. *Микропроцессорная система* — частный случай цифровой электронной системы, предназначенной для обработки входных сигналов и выдачи выходных, это вычислительная или управляющая система, в структуру которой входит *микропроцессор*.

### Электронные цифровые системы

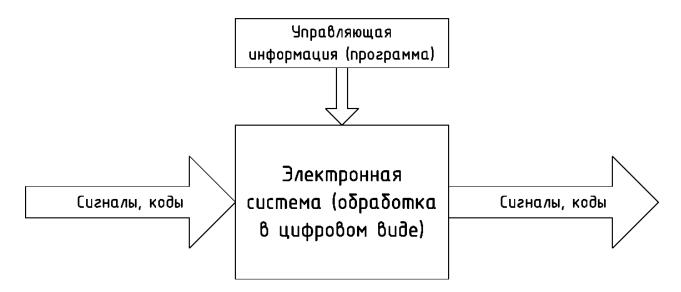

На рис. 1.1 представлена *схема* электронной микропроцессорной системы, осуществляющей обработку информации.

На вход системы могут поступать *аналоговые сигналы*, *цифровые сигналы*, а также *цифровые коды* в виде набора сигналов. На выходе системы могут быть обнаружены сигналы той же природы, только обработанные в соответствии с

алгоритмом программы, выступающей в качестве *управляющей информации* для представленной электронной системы.

Рисунок 1.1. Электронная микропроцессорная система

В случаях, когда система имеет дело с аналоговыми сигналами, используются специальные устройства, такие как *аналогово-цифровой преобразователь* (АЦП) и *цифро-аналоговый преобразователь* (ЦАП) на входе и выходе электронной системы соответственно.

<u>Определение 8</u>. *Традиционная цифровая система* — электронная цифровая система, алгоритмы обработки и хранения информации в которой «жёстко» связаны со схемотехникой системы.

## Примечание:

В данном случае если, например, нужна операция суммирования, необходимо добавить в систему такой элемент, как сумматор (на аппаратном уровне). А это в свою очередь приведёт к новому производственному циклу, включающему проектирование, изготовление и отладку (подробно о процессе производства будет говориться в теме 7).

Традиционная электронная система по своей природе является *специализированной* системой.

## Особенности традиционных цифровых систем

Преимущества специализированной системы:

- **1.** *Отсумствие аппаратной избыточности*. Это ведёт к тому, что система может работать в полную мощность.

- **2.** *Максимально высокое быстродействие*. Быстродействие зависит от состава системы, т.е. от её логических элементов и схемы путей прохождения информации (в специализированной системе схемы путей обычно оптимизированы).

## Недостатки специализированной системы:

**1.** *Отсумствие гибкости*. Переход с одного алгоритма на другой ведёт к изменению аппаратуры.

«Частность» микропроцессорной системы заключается в возможности изменения алгоритма работы, не изменяя аппаратной части. Средством универсальности является управляющая программа. Возможность смены управляющей программы обеспечивается аппаратной избыточностью. Аппаратная избыточность приводит к увеличению стоимости и потребляемой мощности, а также снижению надёжности и быстродействия.

Тенденция сегодняшнего дня — вытеснение традиционных систем на жёсткой логике, вызванное развитием программируемых (микропроцессорных) систем.

## 1.2. Микропроцессор и микропроцессорные системы

### Микропроцессор

Определение 9. *Микропроцессор* — ключевой элемент микропроцессорной системы. Заменяет «жёсткую» логику. Это большая интегральная схема (БИС) (содержащая сотни, тысячи, а то и миллионы элементов и компонентов в одном кристалле полупроводника), выполняющая функции центрального процессора (т.е. устройства, предназначенного для интерпретации программ,

выполняющего основные функции по обработке данных и управлению работой частей системы).

*Встроенный микропроцессор* — микропроцессор, встроенный в устройство и используемый в системе управления этим устройством.

Коммуникационный микропроцессор — специализированная система, выполняющая функции управления сетевыми протоколами в сетевой телеобработке. Обеспечивает повышение производительности сетей.

Секционный микропроцессор — микропроцессор, полученный на основе соединения однотипных 2-, 4- и 8-разрядных микропроцессорных интегральных схем, каждая из которых имеет арифметико-логическое устройство и несколько регистров.

## Работа микропроцессора заключается в выполнении:

- 1. Арифметических функций.

- 2. Логических функций.

- 3. Временного хранения кодов.

- 4. Пересылке кодов между узлами системы.

## Управление работой микропроцессора

<u>Определение 10</u>. *Программа* — набор цифровых кодов, расшифровав которые, процессор узнаёт, что ему надо делать. Программа представляет собой данные, предназначенные для управления конкретными компонентами системы обработки данных в целях реализации определённого алгоритма.

Определение 11. *Система команд* – набор команд, выполняемых процессором. Это полный набор команд, допустимых в машинном языке данного типа вычислительного устройства.

## Характеристики системы команд:

- **1.** *Специализация*, выражается кругом решаемых задач. Может быть *узкой* или *широкой*.

- **2.** *Преимущество*. Выражается быстродействием, гибкостью и удобством использования.

- **3.** *Размер*. Выражается *количеством* занимаемых *разрядов* ячеек памяти.

- **4.** *Время выполнения* отдельных команд. Как правило, выражается в *единицах времени*.

Таким образом, ведя разговор о системе команд конкретного микропроцессора, можно обсуждать ее *специализацию*, т.е. на что она оптимизирована лучше всего (например, на обработку сигналов, передающих звуковую или визуальную информацию, в так называемых *процессорах цифровой обработки* сигналов).

Говоря о преимуществах системы команд, весьма кстати будет вопрос об удобстве её использования, поскольку это напрямую влияет на производительность труда разработчиков программной части микропроцессорной системы.

Такие характеристики, как *размер* системы команд (имеется в виду размер памяти – количество ячеек, занимаемых каждой командой) и *время выполнения* отдельных команд, особый интерес будут представлять для проектировщиков сложных встраиваемых систем реального времени.

### Структура микропроцессора

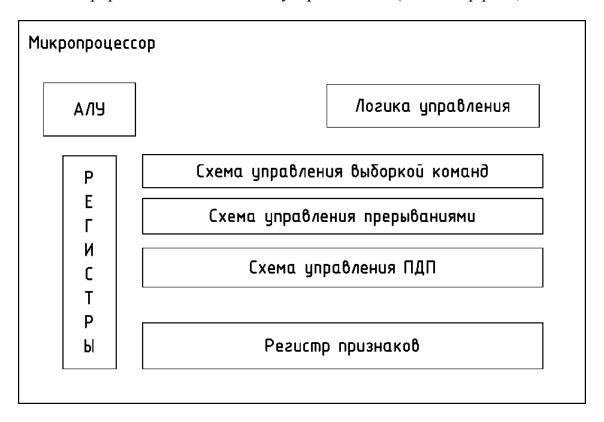

На рис. 1.2 представлена обобщённая структура микропроцессора.

### Структурные составляющие процессора:

- 1. Арифметико-логическое устройство.

- 2. Мультиплексоры.

- **3.** Буферы.

## 4. Регистры.

## Требования к разработчику систем

Требования к разработчику микропроцессорных систем:

**1.** Знание процессора: система команд, доступные режимы работы, правила обмена информацией с внешними устройствами (его интерфейс).

Рисунок 1.2. Структура процессора

## Вопросы

- 1. Что такое электронная система?

- **2.** Как (в какой форме или в каком виде) может быть представлена электронная система?

- 3. Какие отличия (или связи) между узлом, блоком, прибором и комплексом?

- **4.** Дайте определение понятию «задача».

- 5. Что такое быстродействие системы?

- 6. Что такое номинальное быстродействие электронной системы?

- **7.** Дайте определения понятиям «гибкость» и «эксплуатационная гибкость».

- 8. Какие виды избыточности систем вы знаете?

- 9. Какая разница между внутренним и внешним интерфейсом?

- 10. Что является неотъемлемой частью микропроцессорной системы?

- 11. Чем отличается цифровой сигнал от цифрового кода?

- 12. Зачем нужны аналого-цифровой и цифро-аналоговый преобразователи?

- 13. Что понимают под традиционной цифровой системой?

- **14.** Как правильно понять фразу «алгоритм обработки информации жёстко связан со схемотехникой системы»? Можете ли вы привести пример такой связи (или устройства)?

- **15.** Что такое специализированная система? В чём её преимущества и недостатки?

- 16. Что является средством универсальности микропроцессорной системы?

- 17. Что такое микропроцессор? Зачем он нужен?

- **18.** Что такое большая интегральная схема? Почему она называется большой (несмотря на то, что её размер может быть с монету)?

- 19. Что такое центральный процессор?

- **20.** Дайте определения понятиям «встроенный микропроцессор», «коммуникационный микропроцессор», «секционный микропроцессор».

- 21. В чём заключается работа микропроцессора?

- **22.** Что такое программа? В чём разница между алгоритмом, программой и исходным кодом программы?

- **23.** Что такое система команд? Как можно охарактеризовать систему команд. Приведите примеры применения характеристик (например, в рамках дискуссии между инженерами-проектировщиками микропроцессорных систем).

- 24. Какие вы можете выделить структурные составляющие микропроцессора?

- **25.** Какие требования предъявляют к разработчику микропроцессорных систем? Как вы думаете, этих требований достаточно?

## Лекция 2

## 1.3. Коммуникация элементов микропроцессорной системы

## Классическая структура связей

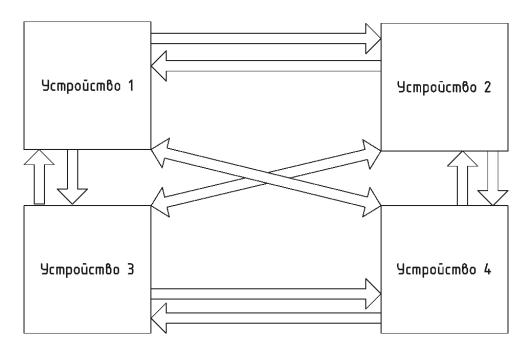

Характеристики классической структуры связей:

- 1. Множество линий связи.

- 2. Различные правила обмена информацией.

На рис. 1.3 представлена классическая структура связей между устройствами.

Рисунок 1.3. Классическая структура связей

## Шинная структура связей

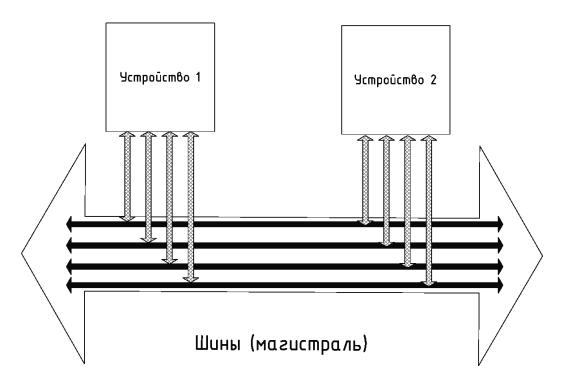

Характеристики шинной структуры связей:

- **1.** Линии связи (у устройств) одни, время связи разное. Такая передача носит название *мультиилексированной передачи*. Результат снижение быстродействия.

- 2. Двунаправленная передача.

**3.** *Одни протоколы обмена информацией*. Таким образом, обеспечивается унификация шинных устройств (т.е. устройств, соединённых единой магистралью).

## Недостатки:

**1.** *Пониженная надёжность*. Неисправность одного устройства может привести к выходу из строя всей системы.

На рис. 1.4 представлена шинная структура связей.

Рисунок 1.4. Шинная структура связей

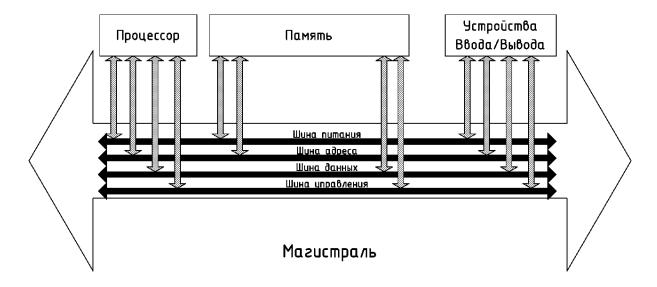

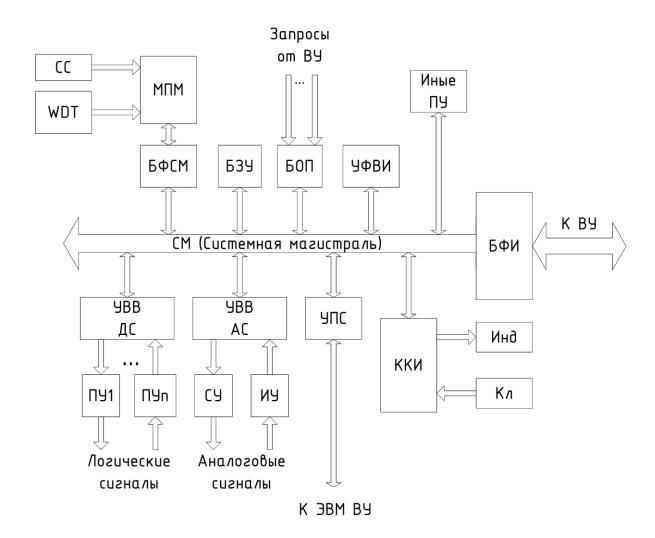

## Структура микропроцессорной системы

## Характеристики микропроцессорной системы:

- **1.** Каждое устройство в микропроцессорной системе, каждая ячейка памяти имеют адрес. Адрес выставляется на *шину адреса*.

- 2. Коды данных выставляются на шину данных.

- **3.** Сигналы *шины управления*: *стробы* (они говорят о том, что код выставлен на шину), сигналы *подтверждения* (часто свидетельствуют о том, что код

получен устройством, участвующим в обмене), *сброс* устройств (рестарт), *тактирование* устройств (синхронизация работы).

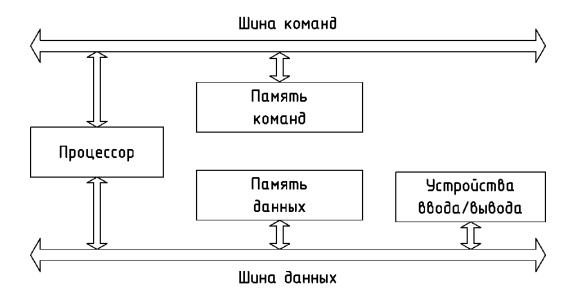

На рис. 1.5 представлена структура микропроцессорной системы.

Рисунок 1.5. Структура микропроцессорной системы

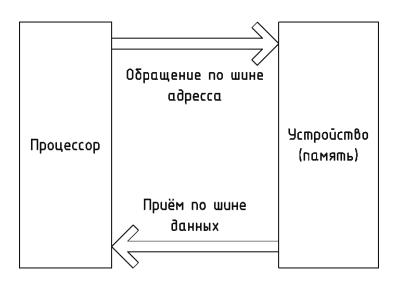

### Обмен информацией

Ввод входного кода в микропроцессорную систему (рис. 1.6):

Рисунок 1.6. Ввод входного кода в микропроцессорную систему

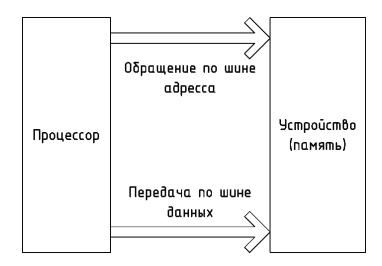

## Вывод выходного кода из микропроцессорной системы (рис. 1.7)

Рисунок 1.7. Вывод выходного кода из микропроцессорной системы

## Виды обмена информацией

1. Программный обмен информацией.

## Характеристики:

- Процессор инициирует все операции обмена информацией.

- На внешние события, не связанные с программой, процессор не реагирует.

- Все сигналы магистрали контролируются процессором.

- **2.** *Обмен по прерываниям*. Применяется в тех случаях, когда требуется реакция процессора на приход внешнего сигнала (от клавиатуры, сетевого адаптера, принтера).

## Способы организации реакции на внешнее событие:

- *Метод опроса флага* (процессор считывает специальную информацию из устройства, которому требуется прерывание процессора; процессор может и не обрабатывать такие «маскируемые» прерывания).

- Прерывание работы процессора (в данном случае процессор обязан приостановить свою работу над текущей задачей и переключиться на ту, которую требует прервавшее его устройство; обычно это так называемые «немаскируемые» прерывания, требующие неотлагательной обработки).

- *Прямой доступ к памяти* (как способ организации реакции на внешнее событие) (процессор отключается от системной магистрали и предоставляет право прервавшему его работу устройству самостоятельно выполнить требуемые операции работы с памятью).

- **3.** *Прямой доступ к памяти* (как вид обмена информацией) (рис. 1.8).

## Характеристики:

- Обмен по шине идёт без участия центрального процессора системы.

- Необходим контроллер прямого доступа к памяти либо в самой микропроцессорной системе, либо в устройстве ввода/вывода.

Рисунок 1.8. Прямой доступ к памяти

## 1.4. Разновидности микропроцессорных систем

## Архитектура с общей шиной для команд и данных

Такая архитектура носит названия — *принстонская* или *архитектура фон Неймана*. В данном случае единая шина позволяет гибко распределять объём между кодами команд и кодами данных (рис 1.9).

Рисунок 1.9. Архитектура фон Неймана (принстонская)

## Архитектура с раздельными шинами команд и данных

Такая архитектура называется гарвардской (рис. 1.10).

## Характеристики:

- 1. Программа размещается в памяти команд, данные в памяти данных.

- 2. Обмен по шинам может идти параллельно во времени.

Рисунок 1.10. Гарвардская архитектура

## Типы микропроцессорных систем

Далее перечисляются типы микропроцессорных систем:

**1.** *Микроконтроллеры*. Узлы системы, выполненные в виде одной микросхемы. Микроконтроллер представляет собой специализированный

микропроцессор для использования в контроллерах внешних устройств или приборов.

**2.** *Контроллеры*. Микропроцессорные системы, выполненные в виде отдельных модулей.

Контроллер в вычислительной машине — специализированный процессор (в отличие от центрального), предназначенный для управления внешними устройствами — накопителями, дисплеями, принтерами. Наличие такого контроллера освобождает центральный процессор от выполнения этих функций.

Контроллер устройства — устройство сопряжения вычислительной машины с внешним устройством и управления обменом между ними. По сравнению с адаптером, такой контроллер выполняет более сложные функции.

- **3.** *Микрокомпьютеры*. Микропроцессорные системы с развитыми средствами сопряжения с внешними устройствами. Микрокомпьютер вычислительная машина малых размеров, созданная на базе микропроцессора. Выделяют встроенные и персональные, настольные и портативные, профессиональные и бытовые.

- **4.** *Компьютеры*. Универсальные микропроцессорные системы. Под компьютером понимают комплекс технических средств, предназначенных для автоматической обработки информации в процессе решения вычислительных и информационных задач.

Стоит сделать несколько замечаний и привести ряд примеров касательно вышеприведённой классификации.

В вычислительных центрах, предоставляющих «высокопроизводительные» услуги, стоят *компьютеры*, объединённые для совместной работы (часто называемые *комплексами*). Так называемые «персональные» компьютеры тоже относятся к классу *компьютеров*.

К *микрокомпьютерам* можно отнести карманные мобильные устройства, устройства воспроизведения и записи цифровой информации, предназначенные для прослушивания и просмотра аудиовизуального содержимого. Сегодня микрокомпьютеры могут быть обнаружены даже в холодильниках (такие холодильники можно программировать по своему усмотрению, выходить в интернет и просматривать телепередачи, а также общаться с друзьями и единомышленниками в специализированных сетевых сообществах).

Как в компьютерах, так и в микрокомпьютерах могут присутствовать контроллеры и микроконтроллеры. Причём микроконтроллеры могут работать в рамках контроллеров. Контроллеры могут быть независимыми устройствами и самостоятельно (почти самостоятельно) управлять внешними устройствами и собирать информацию с объектов. Более подробно о типах контроллеров — в теме 7.

## Вопросы

- 1. Какая основная идея классической структуры связей?

- 2. Перечислите характеристики классической структуры связей.

- 3. Какая основная идея шинной структуры связей?

- **4.** Перечислите характеристики шинной структуры связей. В чём её недостатки (и каковы тогда преимущества)?

- **5.** Что такое мультиплексированная передача данных? Каковы её достоинства и недостатки?

- 6. Что такое протокол обмена информацией?

- 7. Каковы характеристики микропроцессорной системы?

- **8.** Какое отличие между шиной и магистралью. Какие бывают шины (и какие бывают магистрали, привести примеры)?

- **9.** Какие вы можете назвать типы сигналов шины управления (согласны ли вы с такой классификацией)?

- 10. Как происходит ввод входного кода в микропроцессорную систему?

- 11. Как происходит вывод выходного кода из микропроцессорной системы?

- **12.** Перечислите виды обмена информацией, опишите их составляющие и характеристики.

- **13.** Какие вы знаете способы организации реакции на внешнее событие (внешнее относительно микропроцессорной системы)?

- **14.** Что такое принстонская архитектура (есть ли ещё названия у этой архитектуры)?

- 15. Что такое гарвардская архитектура?

- 16. Какие вы знаете типы микропроцессорных систем?

- **17.** Дайте характеристику следующим системам: микроконтроллер, контроллер, микрокомпьютер, компьютер. Где они используются?

# ТЕМА 2. ЦИКЛЫ ОБМЕНА ИНФОРМАЦИЕЙ

## Лекция 3

## 2.1. Циклы обмена информацией

#### Циклы обмена

Ещё одно требование к разработчику микропроцессорных систем — знать *принципы организации обмена информацией по шинам*. Эти знания намного важнее, чем знания особенностей конкретных микропроцессоров, т.к. жизненный цикл магистрали дольше, чем у процессоров.

Обмен информацией происходит в циклах обмена.

<u>Определение 1</u>. **Цикл обмена информацией** – временной интервал, в течение которого происходит выполнение одной элементарной операции обмена по шине (например, пересылка кода данных).

## Типы циклов:

- 1. Цикл записи (вывода). Процессор записывает (выводит) информацию.

- 2. Цикл чтения (ввода). Процессор читает (вводит) информацию.

- **3.** *Цикл чтение-модификация-запись* (ввод-пауза-вывод). Процессор читает информацию из памяти или устройства ввода/вывода, преобразует её и записывает по тому же адресу.

- 4. Цикл прямого доступа к памяти.

- 5. Цикл запроса и предоставления прерывания.

Длительность цикла включает в себя несколько периодов сигнала тактовой частоты (в самом лучшем случае за один такт выполняется один элементарный цикл, а за счёт особой организации микропроцессора можно добиться выполнения команды за один такт).

$$\mathbf{q}_{\mathcal{U}} \ll \mathbf{q}_{mn}$$

где  $\mathbf{Y}$  – частота,  $\mu$  – цикл, mn – тактовый процессор.

## Шины магистрали

### Шина данных

Количество линий связи – количество разрядов.

#### Шина данных определяет:

- 1. Скорость системы.

- **2.** *Эффективность* информационного обмена (качество передачи).

- **3.** Максимально возможное *количество комано* (например, если у нас всего три линии в шине, то максимальное количество распознаваемых команд 8, если не использовать никаких «ухищрений», например передачу команды за несколько циклов).

Шина данных *двунаправленная*. Она также определяет *разрядность всей магистрали*. В таком случае говорят не о внутренней (разрядность регистров и

арифметико-логического устройства), а о внешней (по отношению к процессору) разрядности. Внутренняя и внешняя разрядности могут не совпадать.

## Шина адреса

Шина адреса определяет:

- 1. Допустимый объём прямоадрессуемой памяти.

- $2^{N}$  *количество прямых адресов*, обеспечиваемых шиной адреса, N количество разрядов шины.

Шина адреса может быть *однонаправленной* и *двунаправленной*. В первом случае магистралью управляет только процессор. Во втором случае предусмотрен режим *прямого доступа к памяти*.

Часто применяется *мультиплексирование* шин адреса и данных. В таком случае, циклы передачи адреса и данных происходят по одной шине, но в разное время. Мультиплексирование осуществляется за счёт специальных сигналов, передающихся по шине управления.

## Шина управления

Управляющие сигналы определяют *тип текущего цикла*, фиксируют *моменты стадий цикла*, согласуют работу центрального процессора с работой памяти или устройств ввода/вывода, обслуживают запросы на предоставление прерываний, а также запросы на прямой доступ к памяти.

Линии шины управления могут быть *однонаправленными* или *двунаправленными*.

## Обмен данными

#### Типы обмена данными:

**1.** *Синхронный обмен*. Процессор заканчивает обмен через *установленный временной интервал*.

2. Асинхронный обмен. Процессор заканчивает обмен, когда внешнее

устройство подтверждает выполнение операции специальным сигналом.

В зависимости от типа обмена данными магистрали шин могут быть

синхронными или асинхронными.

2.2. Циклы программного обмена

Обмен по мультиплексированной асинхронной магистрали

Рассмотрим пример обмена по мультиплексированной асинхронной магистрали

**Q-bus** от фирмы DEC. Эта магистраль применялась в компьютерах и

промышленных контроллерах и является хорошим примером для демонстрации

организации асинхронного обмена по мультиплексированной (объединённой)

шине адреса/данных.

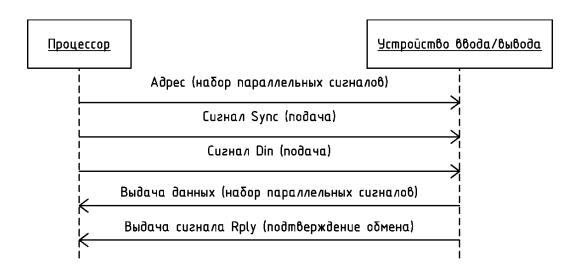

**Цикл чтения** (рис. 2.1)

$\Phi$ аза адреса: 1 – 4 шаг.  $\Phi$ аза данных: 5 – 6 шаг.

Шаги:

1. Процессор выставляет код адреса на шину данных/адреса.

2. Для стробирования используется сигнал Sync, выставляемый процессором

на шину управления.

3. Получив код адреса, распознав его, устройство ввода/вывода или память

готовится к обмену данными.

4. Через некоторое время после сигнала Sync процессор снимает адрес и

начинает фазу данных.

**5.** Процессор выставляет сигнал строба чтения данных **Din**.

6. Устройство выставляет код данных, одновременно подтверждая выполнение

операции сигналом подтверждения обмена **Rply** (сигнал подтверждения

говорит о том, что устройство готово к следующему циклу обмена).

28

**Рисунок 2.1.** Циклы программного обмена по мультиплексированной асинхронной магистрали. Цикл чтения данных

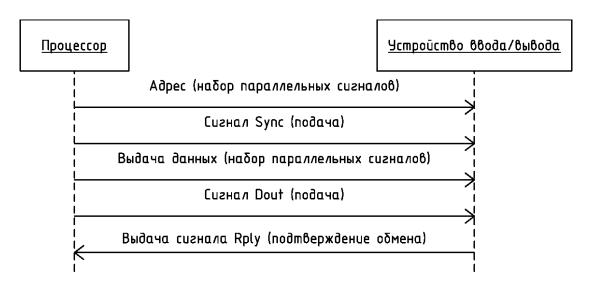

## <u>Цикл записи</u> (рис. 2.2)

**Рисунок 2.2.** Циклы программного обмена по мультиплексированной асинхронной магистрали. Цикл записи

Шаги фазы данных (фаза адреса такая же, как и в предыдущем случае):

- **1.** Процессор выставляет на шину адреса/данных код данных, сопровождает это сигналом строба записи **Dout**.

- **2.** Устройство принимает данные от процессора, формирует сигнал подтверждения **Rply**.

- **3.** Процессор, получив сигнал **Rply**, заканчивает цикл обмена.

- **4.** Процессор снимает сигнал **Dout**.

- **5.** Устройство снимает сигнал **Rply**.

Таким образом, адрес передаётся синхронно, а данные передаются асинхронно.

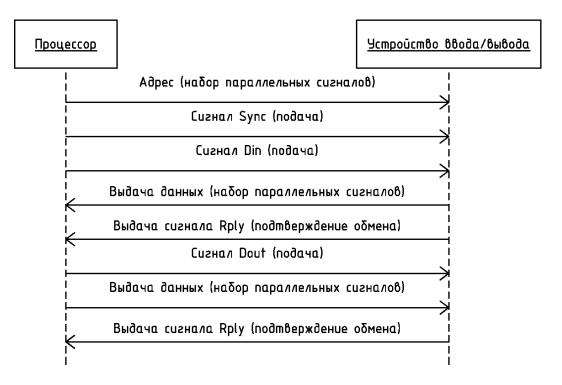

## **Цикл чтение-модификация-запись** (рис. 2.3)

Фаза адреса такая же, как и в предыдущем случае. Моменты фазы данных:

- **1.** Процессор производит сначала чтение, затем запись по одному и тому же адресу.

- 2. Для чтения используется строб **Din**, для записи используется строб **Dout**.

- **3.** На сигнал процессора **Din** устройство выдаёт данные, на сигнал **Dout** устройство принимает данные по шине адреса/данных.

- **4.** Устройство подтверждает выполнение каждой операции сигналом подтверждения **Rply**.

- **5.** Сигнал **Sync** вырабатывается процессором в начале цикла и держится до окончания всего цикла.

**Рисунок 2.3.** Цикл программного обмена по мультиплексированной асинхронной магистрали. Цикл чтение-модификация-запись

## Обмен по синхронной не мультиплексированной магистрали

Рассмотрим другой пример. В данном случае обмен будет происходить по *синхронной не мультиплексированной* магистрали **ISA** от фирмы IBM. Магистраль эта широко используется в персональных компьютерах.

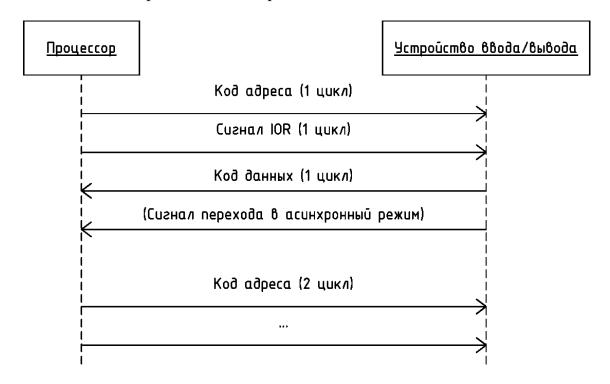

## Циклы чтения (рис. 2.4) и записи (рис. 2.5) одинаковы для фазы адреса:

- **1.** Процессор выставляет код адреса на шину адреса. Сигнал на шине остаётся до конца цикла.

- **2.** Фаза адреса заканчивается (сигнал на шине адреса всё ещё остаётся) с началом строба **IOR** (для чтения) или **IOW** (для записи).

- 3. Устройство принимает адрес, распознаёт его, готовится к обмену.

### Фаза данных (цикл чтения):

- 1. Процессор выставляет сигнал **IOR** (готовность к чтению).

- 2. Устройство выдаёт на шину данных код данных.

- **3.** Через определённое время сигнал **IOR** снимается процессором, чуть позже снимается код адреса с шины адреса.

**Рисунок 2.4.** Цикл программного обмена по синхронной не мультиплексированной магистрали. Цикл чтения

Шина **ISA** допускает *асинхронный обмен*. В этом случае применяется *сигнал готовности канала*. Если устройство не успевает за процессором, оно может сообщить процессору о неготовности и перейти в асинхронный режим. По своему усмотрению устройство может не сообщать о неготовности (если поспевает за процессором).

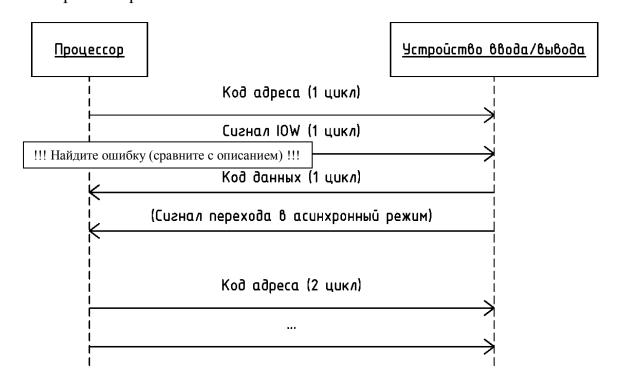

#### Фаза данных (цикл записи):

- **1.** Процессор выставляет на шину данных код данных, сопровождая это стробом записи **IOW**.

- 2. Устройство принимает код данных с шины данных.

- **3.** Если устройство не успевает, оно снимает тот самый сигнал, который говорит процессору о том, что устройство способно поддерживать обмен данными на текущей скорости. Снятие этого сигнал (готовности канала) можно рассматривать как передачу процессору сообщения о том, что устройство не успевает за работой процессора и необходим переход в асинхронный режим.

**Рисунок 2.5**. Цикл программного обмена по синхронной не мультиплексированной магистрали. Цикл записи

## Вопросы

- **1.** Почему знание принципов организации обмена информацией по шинам микропроцессорной системы важнее знания особенностей конкретных микропроцессоров?

- 2. Что такое цикл обмена информацией?

- 3. Дайте пример элементарной операции обмена по шине.

- 4. Какие типы циклов обмена вы знаете? В чём их отличие?

- **5.** Как связаны между собой длительность цикла обмена по шинам микропроцессорной системы и частота тактов процессора?

- 6. Что определяет шина данных?

- 7. Что имеют в виду, когда говорят о разрядности магистрали?

- 8. Что определяет шина адреса?

- **9.** Чем ограничен допустимый объём «прямоадрессуемой» внутренней памяти микропроцессорной системы?

- **10.** Как связано количество разрядов шины адреса и количество прямых адресов внутренней памяти микропроцессорной системы? Как вы думаете, почему адреса называются «прямыми»?

- **11.** Что имеют ввиду, когда говорят, что шина микропроцессорной системы однонаправленная (или двунаправленная)?

- 12. Что такое мультиплексирование шин и за счёт чего оно осуществляется?

- 13. Что определяют сигналы шины управления?

- 14. Какие вы знаете типы обмена данными?

- **15.** Дайте пример мультиплексированной асинхронной магистрали. Где она применяется?

- **16.** Что такое цикл чтения, цикл записи, фаза адреса и фаза данных? Как они связаны друг с другом? В какой последовательности?

- **17.** Дайте пример синхронной не мультиплексированной магистрали. Где она используется?

- **18.** Каким образом синхронная магистраль может перейти в асинхронный режим?

- **19.** Можно ли не меняя аппаратной части микропроцессорной системы из мультиплексированной магистрали сделать не мультиплексированную?

## Лекция 4

## 2.3. Циклы обмена по прерываниям

### Типы прерываний

## Типы прерывания:

- **1.** *Векторные*. Требуют проведения цикла чтения по магистрали. В данном случае устройство передаёт процессору *номер прерывания*. Процессор проводит цикл чтения по магистрали, по шине данных получает код номера прерывания. Такой способ обмена реализован в магистрали **Q-bus**.

- **2.** *Радиальные*. Не требуют цикла обмена по магистрали. В магистрали количество линий запроса прерываний есть *количество различных прерываний*. Отдельное прерывание запрашивается по отдельной линии. В систему включается дополнительная микросхема *контроллера прерываний*. Реализацию описанного метода можно встретить в магистрали **ISA**.

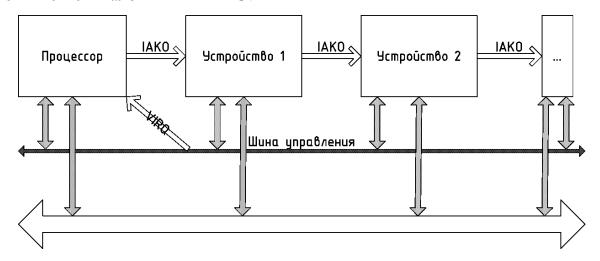

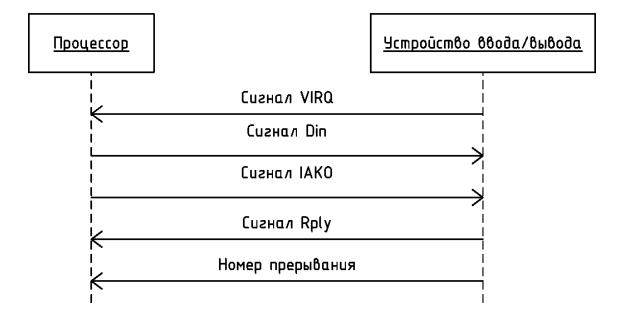

#### Обмен по векторным прерываниям

Рассмотрим <u>обмен по прерываниям на магистрали **Q-bus**</u> (рис. 2.6 - 2.7).

## Шаги обмена:

- **1.** Запрос прерывания осуществляется сигналом **VIRQ**. Этот сигнал формируется одним из устройств.

- **2.** Процессор прекращает выполнение текущей команды и предоставляет прерывание (свои услуги).

- **3.** Процессор выставляет сигнал **Din** (чтение данных) и сигнал **IAKO** (предоставление прерывания).

- **4.** Сигнал **IAKO** последовательно распространяется через все устройства. Устройство, запросившее прерывание, не пропускает сигнал далее.

- 5. Устройство, получив сигнал IAKO, снимает сигнал VIRQ.

- 6. Процессор проводит цикл безадресного чтения номера прерывания.

- **7.** Устройство в ответ на сигналы **Din** и **IAKO** выдаёт на шину адреса/данных код номера прерывания (адрес вектора прерывания) и выставляет сигнал подтверждения **Rply**.

- **8.** Процессор читает код номера прерывания и заканчивает цикл чтения снятием сигналов **Din** и **IAKO**.

**Рисунок 2.6.** Распространение сигналов по магистрали Q-bus

**Рисунок 2.7.** Цикл запроса и предоставления прерывания магистрали Q-bus

#### Обмен по радиальным прерываниям

Рассмотрим пример обмена по прерываниям на магистрали **ISA** (рис. 2.8):

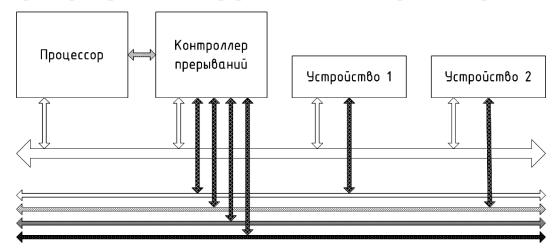

Рисунок 2.8. Магистраль ISA. Обмен по прерываниям

#### Особенности:

- **1.** Процессор общается с контроллером прерываний *по магистрали* для задания режима работы и *вне магистрали* для обработки запросов на прерывания.

- **2.** Сигналы запросов прерываний распределяются между всеми устройствами магистрали.

- 3. На каждую линию прерывания приходится одно устройство.

- 4. Порядок обслуживания прерываний определяет контроллер прерываний.

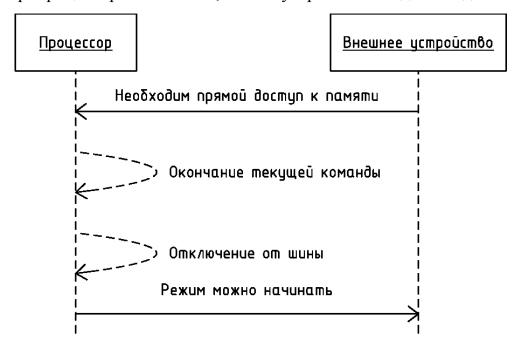

# 2.4. Циклы обмена в режиме прямого доступа к памяти

#### Обмен в режиме прямого доступа к памяти

Принцип – устройство запрашивает прямой доступ к памяти и получает его. Процессор отключается от магистрали.

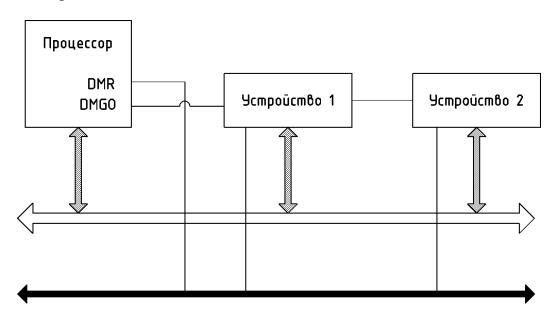

Рассмотрим пример <u>обмена на магистрали Q-bus</u> (рис. 2.9):

#### Шаги обмена:

**1.** Устройство, нуждающееся в прямом доступе к памяти, передаёт сигнал запроса **DMR**.

- **2.** Получив сигнал **DMR**, процессор выдаёт сигнал предоставления прямого доступа к памяти **DMGO**. Сигнал последовательно распространяется через устройства. Устройство, нуждающееся в прямом доступе к памяти, не распространяет сигнал далее.

- **3.** Устройство, получившее прямой доступ к памяти, проводит циклы обмена по магистрали.

Рисунок 2.9. Магистраль Q-bus. Прямой доступ к памяти

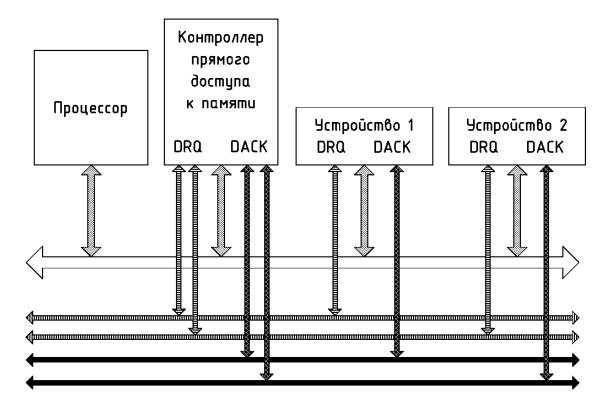

Рассмотрим далее пример обмена на магистрали **ISA** (рис. 2.10).

#### Основные моменты:

- **1.** Сигналы запроса прямого доступа к памяти (**DRQ**) поступают к контроллеру от устройств.

- **2.** Контроллер прямого доступа к памяти распределяет сигналы предоставления доступа (**DACK**) устройствам.

- **3.** К каждому каналу прямого доступа к памяти подключается только одно устройство, запрашивающее доступ.

- **4.** После рассылки сигнала **DACK**, контроллер прямого доступа проводит циклы обмена по магистрали между устройствами.

- **5.** На магистрали **ISA** используются раздельные стробы записи в память **MEMW** и запись в устройства ввода/вывода **IOW**, а также раздельные стробы чтения из памяти **MEMR** и чтения из устройств ввода/вывода **IOR**.

- **6.** Адрес памяти выставляется на шину адреса. Адрес устройств ввода/вывода может быть заменён специальным сигналом.

Рисунок 2.10. Магистраль ISA. Прямой доступ к памяти

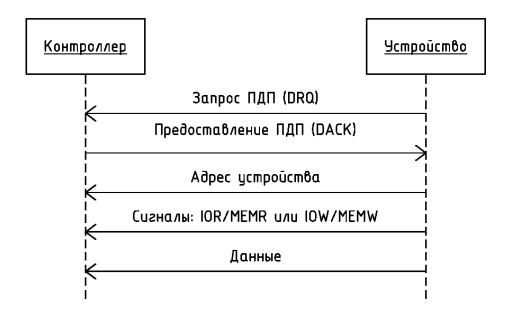

Рисунок 2.11. Магистраль ISA

### Вопросы

- 1. В чём отличие векторных прерываний от радиальных?

- 2. В чём состоят особенности обмена по радиальным прерываниям?

- 3. Зачем нужен контроллер прерываний?

- 4. Зачем нужен контроллер прямого доступа к памяти?

### Промежуточный контроль

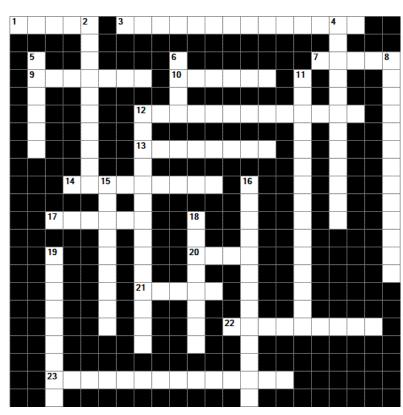

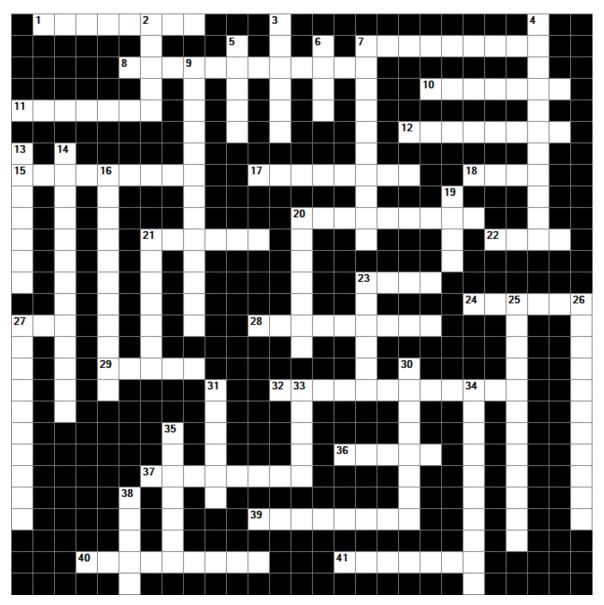

Для закрепления (и проверки) знаний основных понятий и определений студентам предлагается решить кроссворд.

По горизонтали: 1. Структурная составляющая процессора. Показатель скорости выполнения электронной системой своей задачи. Сигнал шины управления, который перезагружает устройства. Структурная составляющая процессора. Требование **10.** электронной системе В набора функций. 12. Структурная составляющая процессора. Совокупность устройств, образующих единое целое. прерываний, требующий проведения чтения цикла магистрали. **17.** Характеристика системы команд, которая выражается количеством занимаемых разрядов ячеек памяти. 20. Совокупность взаимосвязанных элементов

узлов устройства, выполняющих определённую функцию. <u>21.</u> Сигнал шины управления, который говорит о том, что код выставлен на шину. <u>22.</u> Правила обмена информацией между устройствами, участвующими в обмене. <u>23.</u> Микропроцессорная система с развитыми средствами сопряжения с внешними устройствами.

По вертикали: <u>2.</u> Тип прерываний, не требующий цикла обмена по магистрали. <u>4.</u> Степень соответствия возможностей электронной системы решаемой задаче. <u>5.</u> Самостоятельное устройство. <u>6.</u> Часть устройства. <u>8.</u> Характеристика системы команд, которая выражается кругом решаемых задач. Может быть узкой или широкой. <u>11.</u> Узел системы, выполненный в виде одной микросхемы. <u>12.</u> Ключевой элемент микропроцессорной системы. Заменяет «жёсткую» логику. <u>15.</u> Универсальная микропроцессорная система. <u>16.</u> Шина данных определяет \*\*\* информационного обмена. <u>18.</u> Способность электронной системы подстраиваться под определённые задачи. <u>19.</u> Набор цифровых кодов, расшифровав которые, процессор узнаёт, что ему надо делать.

# ТЕМА 3. ФУНКЦИИ УСТРОЙСТВ МАГИСТРАЛИ

### Лекция 5

## 3.1. Устройство процессора

#### Процессор

Микросхема процессора имеет выводы трёх шин: *адреса*, *данных*, *управления*; вывод для подключения внешнего тактового сигнала **CLK**; вывод для сигнала начального сброса **RESET**.

Схема включения процессора представлена на рис 3.1.

Рисунок 3.1. Схема включения процессора

### Смысл буферных микросхем:

- 1. Демультиплексирование сигналов.

- 2. Согласование протоколов обмена.

После включения питания процессор переходит в первый адрес программы начального пуска и выполняет эту программу, находящуюся в постоянной

памяти. Далее процессор выполняет программу из ПЗУ или ОЗУ (например, программу загрузчика операционной системы).

### Схема управления выборкой команд

Схема управления выборкой команд необходима для чтения команд и их дешифрации.

В 16-разрядных процессорах появился конвейер (очередь) команд, позволяющий выбирать несколько следующих команд, пока выполняется предыдущая команда.

### Арифметико-логическое устройство

### Выполняемые операции:

- 1. *Логические* операции: И (AND), ИЛИ (OR), исключающее ИЛИ (XOR).

- **2.** *Арифметические* операции: сложение (+), вычитание (-), умножение (\*), деление (/).

### Пути повышения производительности:

- 1. Довести время выполнения команды до одного такта.

- **2.** Уменьшить количество выполняемых АЛУ команд (т.е. сократить сложность устройства).

- 3. Использование нескольких параллельно работающих АЛУ.

#### Регистры

### Функции регистров:

- 1. Временное хранение кодов.

- 2. Предоставление ячеек очень быстрой памяти.

*Внутренняя разрядность процессора* – разрядность регистров и АЛУ. Может не совпадать с внешней разрядностью (т.е. разрядностью магистрали).

### Подходы к назначению регистров:

- **1.** Отведение регистру строго определённой функции (как в процессорах от Intel).

- **2.** Равноправие регистров (пример процессор DEC T-11).

- **3.** Промежуточное решение (яркий пример процессор Motorola MC68000).

### Регистр признаков (состояния):

- 1. Содержимое слово состояния процессора.

- **2.** Каждый бит флаг, который содержит информацию о результате выполнения предыдущей команды.

- **3.** Бывают флаги управления, определяющие режим выполнения некоторых команд.

#### **Управление**

### Схема управления прерываниями:

- 1. Обрабатывает запросы на прерывание.

- 2. Определяет адрес начала программы обработки прерывания.

- **3.** Сохраняет в памяти текущее состояние регистров процессора. Обеспечивает переход к программе обработки прерывания.

# Схема управления ПДП (функции):

1. Приостановка работы процессора.

# Логика управления (функции):

- 1. Организация взаимодействия узлов процессора.

- 2. Перенаправление данных.

- 3. Синхронизация работы процессора с внешними сигналами.

- 4. Реализация процедур ввода и вывода информации.

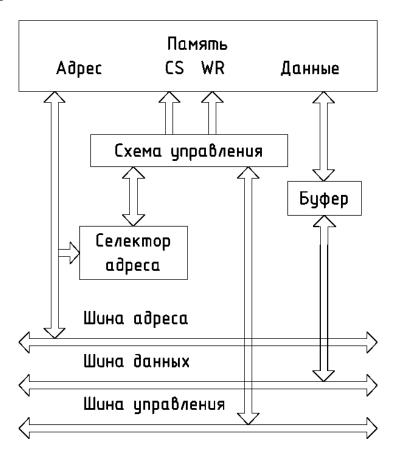

#### 3.2. Память

### Устройство памяти

### Характеристики устройства памяти:

- 1. Временное или постоянное хранение данных и команд.

- 2. Информация хранится в ячейках (у каждой ячейки есть адрес).

- **3.** Для подключения к системной магистрали используются блоки сопряжения: дешифратор (*селектор*) адреса, схема обработки управляющих сигналов, буферы данных.

На рис. 3.2 представлена схема подключения устройства памяти к магистрали микропроцессорной системы.

Рисунок 3.2. Схема включения памяти

#### Особенности:

- **1.** Память обычно состоит из модулей. Каждый модуль работает в своей области пространства.

- **2.** Селектор адреса (дешифратор) определяет, какая область адресов пространства памяти отведена данному модулю памяти.

- **3.** Схема управления вырабатывает в нужные моменты сигналы разрешения работы памяти (**CS**) и сигналы разрешения записи в память (**WR**).

- 4. Буфер является посредником между памятью и магистралью.

### Память программы начального запуска:

- 1. Программа запуска находится в ПЗУ или флэш-памяти.

- **2.** Программа запуска считывается во время включения питания или перезапуска системы.

### Стек (функции и характеристики):

- 1. Часть оперативной памяти. Временное хранение данных.

- 2. Заданный и неизменный способ адресации.

- **3.** Запись в стек по адресу, содержащемуся в регистре указателя стека, после чего содержимое указателя стека уменьшается (на длину записываемых в стек данных). Чтение из стека из адреса, содержащегося в указателе стека, после чего содержимое указателя стека увеличивается.

- **4.** В стеке можно прятать не только содержимое внутренних регистров процессора, но и содержимое регистра признаков, можно хранить произвольные данные.

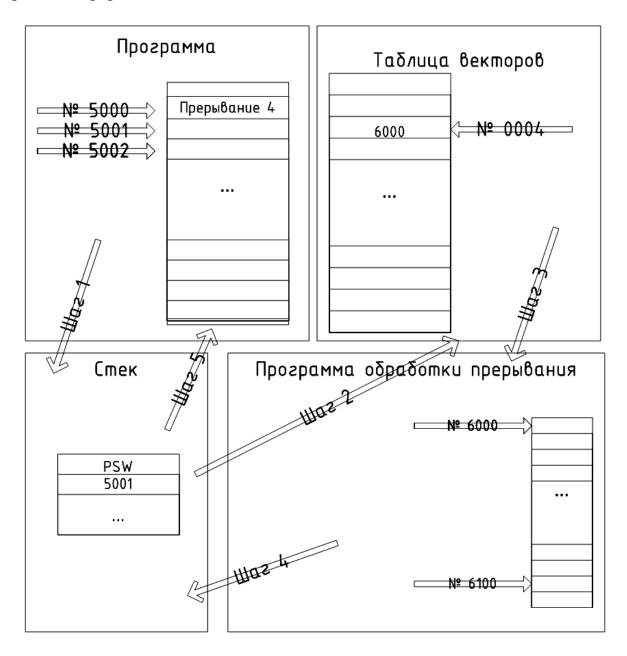

### Таблица векторов прерывания:

- **1.** Прерывания обрабатываются через таблицу векторов (указателей) прерываний.

- **2.** Таблица векторов содержит адреса начала программ обработки прерываний, которые называются *векторами*.

- **3.** Обычно таблица располагается в начале пространства памяти (ячейках памяти с малыми адресами).

- **4.** В случае аппаратных прерываний номер прерывания задаётся устройством (передаётся по шине данных), запросившем прерывание (*векторное прерывание*) или номером линии запроса прерываний (*радиальное прерывание*).

- **5.** В конце программы обработки прерываний располагается команда выхода из прерывания, после которой процессор возвращается к выполнению прерванной основной программы (адрес возврата извлекается из стека).

- **6.** Параметры процессора на время выполнения программы обработки прерывания сохраняется в стеке (в том числе и адрес следующей после текущей команды).

### Алгоритм обработки прерывания на примере:

- **Шаг 1**. Процессор выполняет программу. Текущая команда расположена по адресу 5000. Поступает запрос прерывания с номером 4.

- **Шаг 2**. Процессор заканчивает выполнение команды по адресу 5000. Сохраняет в стеке значение счётчика команд (5001 т.е. адрес следующей команды) и текущее значение **PSW** (слово состояния процессора).

- **Шаг 3**. Процессор читает из адреса 4 памяти код вектора прерывания. Он равен 6000. Процессор переходит в адрес 6000 и выполняет программу обработки прерывания.

- **Шаг 4**. Дойдя до места, где программа обработки заканчивается (в нашем примере 6100), процессор возвращается к выполнению прерванной программы.

- **Шаг 5**. Процессор извлекает из стека значение адреса 5001 и **PSW**. Процессор читает команду по адресу 5001 и последовательно выполняет команды программы.

Возможно многократное вложение прерываний, когда во время выполнения программы обработки прерывания поступает новый запрос на прерывание.

В сложных случаях таблица векторов прерываний содержит дескрипторы прерываний. Результат обработки дескриптора — адрес начала программы обработки прерывания.

Рисунок 3.3. Алгоритм обработки прерывания

### Память устройств, подключенных к шине:

Подходы к разделению адресов памяти и устройств:

- Выделение в общем адресном пространстве области адресов для устройств ввода/вывода.

- Разделение адресных пространств памяти и устройств ввода/вывода.

В 1-м случае используются те же команды, что и при работе с памятью. Объём памяти уменьшается.

В 2-м случае применяются специальные команды и специальные стробы обмена по магистрали. Память не сокращается.

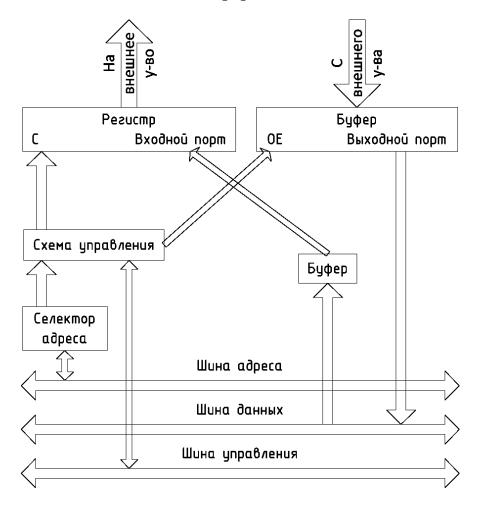

#### Устройства ввода/вывода:

- 1. Обмен информацией осуществляется по тем же принципам, что и с памятью.

- **2.** Устройства ввода/вывода взаимодействуют не только процессором, но и с внешними устройствами: цифровыми, аналоговыми.

### Структура устройств ввода/вывода (рис 3.4):

- 1. Схема управления для обработки стробов обмена.

- **2.** *Входной порт* (имеется в виду, что он «входной» для устройства ввода/вывода) параллельный регистр, в который процессор записывает информацию.

- **3.** *Выходной порт* однонаправленный буфер, через который процессор читает информацию.

Входной порт и выходной могут комбинироваться в один вход/выход.

- **4.** *Селектор адреса* распознаёт адрес со стороны магистрали.

- **5.** Схема управления выдаёт внутренние стробы обмена в ответ на магистральные стробы обмена.

- 6. Буфер осуществляет согласование шины данных с устройством.

Из шины данных данные записываются в регистр по сигналу  $\mathbf{C}$  и выдаются на внешнее устройство. Сигнал  $\mathbf{OE}$  — разрешение на чтение с внешнего устройства.

### Группы устройств ввода/вывода:

- 1. Устройства интерфейса пользователя.

- 2. Устройства ввода/вывода для длительного хранения информации.

- 3. Таймерные устройства.

- 4. Устройства для подключения к информационным сетям.

Рисунок 3.4. Структура устройств ввода/вывода

# Вопросы

- **1.** Какие выводы (контакты, разъёмы) могут быть обнаружены на микросхеме процессора?

- 2. Что происходит при включении питания процессора?

- 3. Зачем нужна схема управления выборкой команд?

- 4. Что такое конвейер команд?

- 5. Какие операции выполняет арифметико-логическое устройство?

- 6. Как можно повысить производительность процессора?

- **7.** Как вы думаете, почему производительность процессора можно сделать выше, если уменьшить количество команд, выполняемых арифметикологическим устройством?

- 8. Что такое внутренняя разрядность процессора?

- 9. Какие существуют подходы к назначению регистров процессора?

- 10. Что такое регистр признаков? Какая от него польза?

- 11. Каковы функции схемы управления прерываниями?

- 12. Каковы функции схемы управления прямым доступом к памяти?

- 13. Что делает схема логики управления?

- 14. Перечислите характеристики устройства памяти.

- 15. Что определяет селектор (дешифратор) адреса?

- 16. Что вы можете сказать о памяти программы начального запуска?

- **17.** Что такое стек?

- 18. Что вы знаете об обработке прерываний?

- 19. Что вы можете сказать об устройствах ввода/вывода?

# ТЕМА 4. АДРЕСАЦИЯ ОПЕРАНДОВ И РЕГИСТРЫ ПРОЦЕССОРА

### Лекция 6 (часть 1)

# 4.1. Адресация операндов

#### Адресация

#### Общие моменты:

- **1.** Система команд определяет логику работы процессора и его реакцию на те, или иные комбинации внешних событий.

- **2.** Каждая команда, выбираемая из памяти процессором, определяет алгоритм поведения процессора на ближайшие несколько тактов.

- **3.** Код команды говорит о том, какую операцию предстоит выполнить процессору и с какими операндами, где взять исходную информацию для выполнения команды и куда поместить результат.

- 4. Процессор обычно узнаёт размер команды из первого прочитанного байта.

- **5.** Код команды расшифровывается и преобразуется в набор микроопераций, выполняемых отдельными узлами процессора.

#### Методы адресации

<u>Определение 1</u>. *Методы адресации* – методы, с помощью которых по коду команд можно определить (задача микропроцессора), откуда брать входной операнд и куда помещать выходной.

### Непосредственная адресация

Операнд находится в памяти непосредственно за кодом команды. Операнд обычно представляет собой константу.

### Прямая (абсолютная) адресация

Операнд находится в памяти по адресу, код которого находится внутри программы сразу же за кодом команды.

#### Регистровая адресация

Операнд находится во внутреннем регистре процессора.

#### Косвенно-регистровая (косвенная) адресация

Во внутреннем регистре процессора находится не сам операнд, а его адрес в памяти.

### Автоинкрементная адресация

Отличается от косвенной адресации тем, что после выполнения команды содержимое регистра увеличивается.

Данный метод даёт удобство при обработке кодов из массива данных (в этом случае содержимое регистра увеличится на размер элемента массива).

#### Автодекрементная адресация

Данный тип адресации противоположен типу автоинкрементной адресации.

Совместное использование автоинкрементной и автодекрементной адресаций позволяет организовать память стекового типа.

### Индексные методы адресации

Адрес операнда вычисляется путём прибавления к содержимому регистра заданной константы (индекса).

### 4.2. Сегментирование памяти

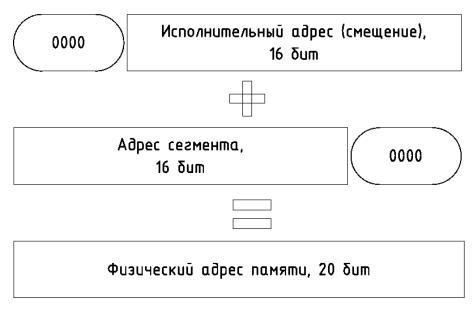

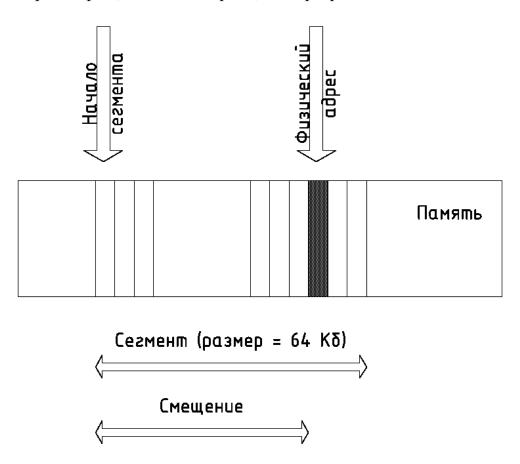

### Сегментирование в Intel 8086

- **1.** Память системы представлена в виде сегментов, размером по 64 Кб, их положение в пространстве памяти можно изменять программным путём.

- 2. Для хранения кодов адресов памяти используются пары регистров:

- Сегментный регистр определяет адрес начала сегмента (положение в памяти).

- Регистр указателя (смещения) определяет положение рабочего адреса внутри сегмента.

- **3.** Шина адреса 20-разрядная. Физический адрес формируется так, как показано на рис 4.1.

- **4.** Сегмент начинается только на 16-байтной границе памяти, т.к. адрес начала сегмента имеет 4 младших нулевых разряда (адрес кратен 16). Эти границы сегментов называются *границами параграфов*.

- **5.** Суть введения сегментирования внутренние регистры процессора 16разрядные, а физический адрес памяти – 20-разрядный (поскольку шина

адреса – 20-разрядная). Следовательно, это нужно для того, чтобы адресовать больше памяти.

**Рисунок 4.1.** Сегментирование в Intel 8086

В процессоре **Motorola MC 68000** такой проблемы не возникает, т.к. внутренние регистры (как и магистраль) – 32-разрядные.

Рисунок 4.2. Сегментирование

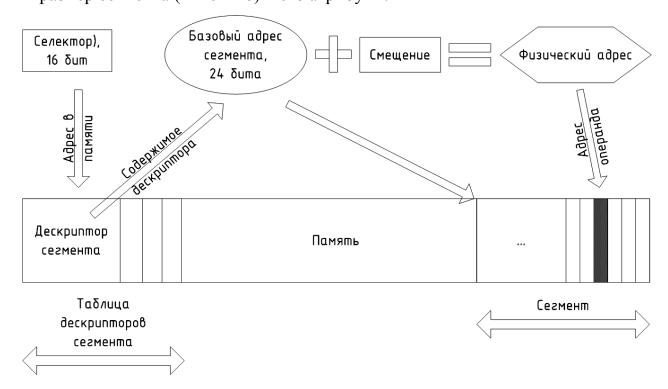

#### Метод сегментирования в Intel 80286

В защищённом режиме (рис. 4.3):

- 1. Содержание сегментного регистра код селектора.

- **2.** Код селектора определяет адрес в памяти, по которому хранится дескриптор сегмента (в таблице дескрипторов).

- **3.** Дескриптор сегмента содержит базовый адрес сегмента (24 бит, что обеспечивает адресацию 16 Мб физической памяти,  $2^{24} = 16^{777}216$ ), размер сегмента (1 64 Кб) и его атрибуты.

**Рисунок 4.3.** Сегментирование в Intel 80286

#### Адресация памяти и сегментирование в Intel 80386

**1 этап** – вычисляется эффективный адрес (32 разряда): база (начало массива) + индекс (элемент массива) + смещение (сдвиг относительно элемента массива), в некоторых случаях индекс умножается на масштаб (1, 2, 4, 8) (в этом случае масштаб задаёт область, в рамках которой имеет смысл применять смещение).

- **2 этап** блок сегментации вычисляет *линейный адрес* (32 разряда): базовый адрес сегмента (содержание сегментного регистра) + эффективный адрес (полученный на предыдущем этапе).

- **3** этап получение физического адреса (32 бита): блок страничной переадресации преобразует линейный адрес. Таким образом, линейный адрес переводится в физический, страницами по 4 байта.

### 4.3. Регистры процессора

### Регистры процессора Intel 8086

В данной модели процессора 14 регистров, по 16 бит каждый.

### Регистры данных:

- **1. АХ** (аккумулятор) умножение, деление, обмен с устройствами ввода/вывода.

- **2. BX** (база) базовый регистр в вычислениях адреса.

- 3. СХ (счётчик) счётчик циклов.

- **4. DX** (данные) определение адреса ввода/вывода.

#### Сегментные регистры:

- **1. CS** сегмент команд.

- **2.** DS сегмент данных.

- 3. ES дополнительный сегмент данных.

- **4. SS c**eгмент **c**тека.

<u>Регистры-указатели</u> (определяют смещение в пределах сегмента): SP, BP, SI, DI, IP.

- **1.** CS + IP -счётчик команд процессора.

- **2.** SS + SP -указатель стека.

- 3. SI, DI используются в операциях со строками.

<u>Регистр состояния процессора</u> – **FLAGS**, 16 разрядов, часто используемые разряды:

- **1. CF** перенос (старшего бита).

- **2. PF** чётность (чётное количество единиц младшего байта, например **AL** регистра **AX**).

- 3. АГ дополнительный перенос (перенос из третьего бита).

- **4. ZF** нулевой результат.

- **5. SF** флаг знака.

- **6. TF** пошаговый режим (используется при отладке программ).

- **7. IF** разрешение аппаратных прерываний.

- 8. DF флаг направления при строковых операциях.

- **9. ОГ** флаг переполнения (произошла установка или сброс знакового бита).

Флаги устанавливаются и очищаются в зависимости от результата предыдущей операции или специальными командами процессора.

### Вопросы

- 1. Как связана адресация и система команд?

- 2. Что такое методы адресации?

- 3. Какие вы знаете методы адресации?

- **4.** В чём смысл непосредственной адресации? Что такое операнд? Что такое константа?

- **5.** Почему прямая адресация называется «прямой»?

- **6.** Что такое сегментация?

- 7. Что такое граница параграфа?

- **8.** Назовите группы регистров процессора Intel 8086.

- 9. Что вы знаете о регистре состояния процессора Intel 8086?

# **ТЕМА 5. СИСТЕМА КОМАНД ПРОЦЕССОРА**

### Лекция 6 (часть 2)

### 5.1. Команды процессора

#### Команды пересылки данных

#### Функции:

- 1. Загрузка (запись) содержимого во внутренние регистры процессора.

- 2. Сохранение в памяти содержимого внутренних регистров процессора.

- 3. Копирование содержимого из одной области памяти в другую.

- 4. Запись в устройства ввода/вывода и чтение из них.

### Примеры команд:

- **1.** MOV, MOVВ байтовая пересылка.

- **2. LOAD** для загрузки регистров.

- 3. **PUSH/POP** работа со стеком.

- **4.** MOVS, MOVSВ для цепочной пересылки данных.

- **5. IN/OUT** для работы с устройствами ввода/вывода.

- **6. INS/OUTS** цепочный ввод/вывод.

- 7. SWAP обмен между двумя половинами одного регистра.

#### Арифметические команды

<u>Операции с фиксированной запятой</u> (работают как с числами со знаком, так и с числами без знака):

- **1. ADD** сумма двух кодов.

- **2. SUB** разность двух кодов.

- **3. MUL** произведение. **IMUL** произведение с учётом знака.

- **4. DIV** деление. **IDIV** деление с учётом знака.

<u>Операции с плавающей запятой</u> (формат числа – порядок, мантисса): вычисление тригонометрических, логарифмических функций.

### Прочие команды:

- 1. Команда очистки CLR запись нулевого кода в регистр или ячейку памяти.

- **2. INC** команда инкремента.

- 3. DEC команда декремента.

- **4. СМР** сравнение операндов изменяет биты в регистре состояния процессора.

#### Логические команды

Коды операндов рассматриваются как набор битов.

### Операции:

- 1. Логическое И (AND), логическое ИЛИ (OR), сложение по модулю 2 (XOR).

- 2. Логические, арифметические и циклические сдвиги.

- 3. Проверка битов.

- 4. Установка и очистка битов регистра состояния процессора.

### Примеры:

- **1. AND** принудительная очистка заданных битов.

- **2. ОR** принудительная установка заданных битов.

- **3. ХОК** инверсия заданных битов.

- **4. TST** проверка операнда на равенство нулю и на знак.

- **5. BIT** проверка отдельных битов.

#### Команды переходов

### Предназначение:

- **1.** Организация циклов, ветвлений, вызовов подпрограмм и т.д. Нарушение последовательного хода выполнения программы.

- **2.** Команды записывают в регистр-счётчик команд новое значение, тем самым вызывая переход процессора к определённой команде в памяти. Если предусмотрен возврат, то текущие параметры процессора сохраняются в стеке.

### Команды перехода без возврата:

- 1. Безусловных переходов.

- 2. Условных переходов.

Для проверки условий перехода применяется команда сравнения — **СМР**, предшествующая команде условного перехода.

**INT** — вызов прерываний, команда перехода с возвратом. Сохраняет содержимое регистра состояния процессора в стеке.

**IRET/RTI** – возврат из подпрограммы, вызванной командой прерывания.

### Факторы, влияющие на быстродействие процессора:

- **1.** *Тактовая частота процессора* скорость выполнения команд, однако разные процессоры выполняют одинаковые команды за разное количество тактов. Это зависит от сложности команды и методов адресации операндов.

- **2.** *Структура системы команд процессора*. На одну операцию может понадобиться одна или несколько команд.

- **3.** *Методы адресации*, наличие сегментированной памяти, способы взаимодействия с устройствами ввода/вывода.

- 4. Разрядность процессора.

- 5. Объём системной памяти.

#### Вопросы

- 1. Что такое команды пересылки данных?

- 2. Какие вы знаете команды пересылки данных?

- 3. Какие вы знаете арифметические команды?

- 4. Какие ещё команды вы знаете?

- 5. Зачем нужны команды переходов?

- 6. Назовите факторы, влияющие на быстродействие процессора.

# **ТЕМА 6. ОРГАНИЗАЦИЯ МИКРОКОНТРОЛЛЕРОВ**

### Лекция 7

### 6.1. Устройство микроконтроллера

#### Классы микроконтроллеров

Микроконтроллер объединяет в *одном кристалле*: центральный процессор, ПЗУ, ОЗУ, порты ввода/вывода, таймеры.

### Классы микроконтроллеров:

- 1. 8-разрядные микроконтроллеры для встраиваемых систем.

- **2.** *16 и 32 разрядные* микроконтроллеры.

- 3. *Цифровые сигнальные процессоры* (DSP).

Применимость 1-го класса – промышленность, бытовая и компьютерная техника.

Фирмы производители – Motorola, Microchip, Intel, Zilog, Atmel.

### Отличительные признаки 8-разрядных микроконтроллеров:

- 1. Модульная организация.

- 2. Закрытая архитектура (отсутствие линий магистрали на выводах корпуса).

- 3. Использование типовых функциональных модулей: таймеры, АЦП, ....

- 4. Расширение числа режимов работы периферийных модулей.

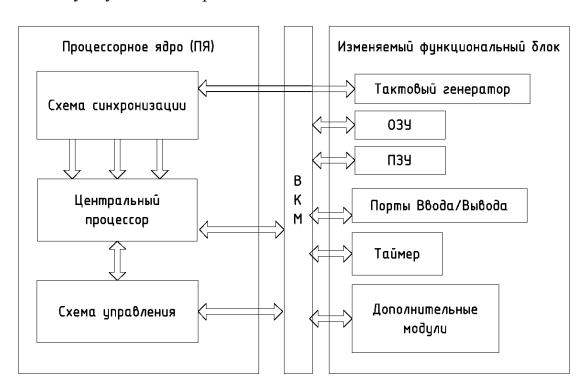

#### Модульная организация микроконтроллера

### Процессорное ядро (состав):

- 1. Центральный процессор.

- **2.** Внутренняя контроллерная магистраль (ВКМ) в составе шин адреса, данных, управления.

- 3. Схема синхронизации микроконтроллера.

- 4. Схема управления режимами работы.

### Изменяемый функциональный блок:

- 1. Модули памяти.

- 2. Порты ввода/вывода.

- 3. Модули тактовых генераторов.

- 4. Таймеры.

- 5. Дополнительные модули: компаратор напряжения, АЦП.

Каждый модуль учитывает протокол ВКМ.

Рисунок 6.1. Организация микроконтроллера

В каждой *модели* одной *серии* микроконтроллеров используют одинаковое процессорное ядро. В разных моделях одной серии микроконтроллеров используют различные изменяемые функциональные блоки.

## Производительность процессорного ядра микроконтроллера определяется:

- 1. Набором регистров для хранения промежуточных данных.

- 2. Системой команд процессора.

- 3. Способами адресации операндов в пространстве памяти.

- 4. Организацией процессов выборки и исполнения команды.

Используют один из двух принципов построения процессоров: CISC, RISC.

### CISC (характеристики):

- **1.** Примеры: Intel с ядром MCS-51, семейства HC05, HC08, HC11 фирмы Motorola.

- 2. Команды переменной длины.

- 3. Различные способы адресации операндов.

- **4.** Время выполнения команды от 1 до 12 тактов (команды могут быть различной сложности).

### RISC (характеристики):

- 1. Примеры: AVR от Atmel, PIC16 и PIC17 фирмы Microchip.

- 2. Фиксированная длина команд.

- **3.** Выборка и исполнение команд может производиться за один такт процессора.

Более сложная система команд (CISC) иногда позволяет реализовать более эффективный способ выполнения операции.

В микроконтроллере применяется одна из двух архитектур микропроцессорных систем: *принстонская* (фон Неймановская) и *гарвардская*.

Архитектура фон Неймана – гибкость и универсальность.

Гарвардская архитектура — сокращение длины команд, ускорение поиска информации в памяти данных, возможность реализации параллельных операций, недостаточная гибкость для реализации некоторых программных процедур.

# 6.2. Система команд микроконтроллера

#### Система команд

#### Виды команд:

- **1.** Арифметические и логические команды, менее развиты, чем у микропроцессора.

- 2. Команды переходов.

Следующие команды более развиты, чем у микропроцессоров:

- 3. Команды битового управления (разрядами регистров).

- **4.** Команды управления ресурсами (настройка режимов работы портов ввода/вывода, управление таймером и т.п.).

- 5. Команды пересылки данных.

#### Память программ

Обычно это ПЗУ для хранения команд и констант. Энергонезависимая память.

### Типы:

- **1.** ПЗУ *масочного типа* (mask-ROM). Содержимое ячеек заносится при изготовлении с помощью масок и не может быть, в последствие, заменено. Высокая надёжность хранения информации (программирование в заводских условиях, контроль результата).

- **2.** ПЗУ, *программируемые пользователем*, *с ультрафиолетовым стиранием* (EPROM). Программируется электрическими сигналами и стирается с помощью ультрафиолетового облучения. Допускает многократное программирование.

- **3.** ПЗУ, *программируемые пользователем*, *с электрическим стиранием* (EEPROM). Стирание и программирование происходит, не снимая микроконтроллер с платы. Ограниченный объём памяти.

- **4.** ПЗУ, однократно программируемые пользователем (OTPROM).

- **5.** *Флэш-память* (flash-ROM). В EEPROM стирание производится отдельно для каждой ячейки. Здесь стирание производится блоками.

#### Память данных

На основе статического ОЗУ. Содержимое сохраняется при снижении тактовой частоты.

<u>Определение 1</u>. *Напряжение хранения информации* — напряжение, при котором работа программы выполняться не будет, но информация в ОЗУ сохраняется. Нужно для возможности перевода микроконтроллера на питание от автономного источника (батареи).

### 6.3. Дополнительные вопросы организации микроконтроллеров

### Регистры микроконтроллера

Регистры процессора: аккумулятор, регистры состояния, индексные регистры.

Регистры управления: управление прерыванием, таймеры.

<u>Регистры, обеспечивающие ввод/вывод данных</u>: регистры данных, управления параллельным, последовательным и аналоговым вводом/выводом.

В некоторых микроконтроллерах все регистры и память данных располагаются в одном адресном пространстве. В других — отдельное пространство у ввода/вывода (регистров) от общего пространства памяти (преимущество процессорам с гарвардской архитектурой, обеспечивается возможность считывать команды из памяти во время обращения к регистру ввода/вывода).

#### Стек микроконтроллера

В фон Неймановской архитектуре единая область памяти используется и для реализации стека. Производительность снижается (нет возможности доступа к различным видам памяти).

В гарвардской архитектуре стековые операции производятся в специально выделенной для этой цели памяти.

#### Внешняя память

Микроконтроллер может содержать специальные аппаратные средства для подключения внешней памяти.

Более часто используются порты ввода/вывода для подключения внешней памяти, обращение к памяти реализуется программными средствами. В этом случае происходит снижение быстродействия.

### Порты ввода/вывода

#### Общие моменты:

- **1.** Линии ввода/вывода объединены в многоразрядные (чаще 8-разрядные) параллельные *порты* ввода/вывода.

- **2.** В памяти микроконтроллера каждому порту ввода/вывода соответствует свой адрес регистра данных (поэтому такие регистры ещё называют портами).

- **3.** Обращение к регистру данных порта ввода/вывода производится теми же командами, что и обращение к памяти данных.

- **4.** В некоторых микроконтроллерах отдельные разряды портов могут быть опрошены или установлены специальными командами.

### Типы параллельных портов:

- 1. Однонаправленные порты (только ввод или только вывод информации).

- **2.** *Двунаправленные порты*. Ввод или вывод определяется в процессе инициализации микроконтроллера.

- **3.** *Порты с альтернативной функцией* (мультиплексированные порты). Отдельные линии используются разными встроенными периферийными устройствами.

Порты производят временное согласование функционирования микроконтроллера и объекта управления.

<u>Типы алгоритмов обмена информацией между микроконтроллером и внешним устройством через порты ввода/вывода:</u>

- 1. Режим простого программного ввода/вывода.

- 2. Режим ввода/вывода со стробированием.

- 3. Режим ввода/вывода с полным набором сигналов подтверждения обмена.

#### Модуль прерываний микроконтроллера

Используются те же принципы, что и в микропроцессорных системах.

### Источники внутренних запросов прерываний:

- 1. Переполнение таймеров/счётчиков.

- **2.** Готовность памяти EEPROM.

- **3.** Сигналы от дополнительных модулей микроконтроллера, включая завершение передачи или приёма информации по одному из последовательных портов.

- **4.** Запрос прерывания поступает на обработку, если прерывания разрешены и разрешено прерывание по данному запросу.

### Аппаратные прерывания с немаскируемым характером:

- 1. Включение питания.

- 2. Подача сигнала «сброс».

- 3. Переполнение сторожевого таймера.

### Режимы работы микроконтроллера

- 1. Активный режим. Основной режим, когда доступны все ресурсы.

- **2. Режим ожидания**. Центральный процессор прекращает работу, периферийные модули продолжают функционировать.

- **3. Режим останова**. Работу прекращают: центральный процессор и периферийные модули.

- 2,3 режимы пониженного электропотребления.

### Вопросы

- 1. Из чего состоит микроконтроллер?

- **2.** Какие основные отличительные признаки 8-разрядных микроконтроллеров вы можете назвать?

- 3. Из чего состоит процессорное ядро?

- 4. Что такое изменяемый функциональный блок?

- **5.** Что такое «модель» микроконтроллера? Чем она отличается от «серии»?

- **6.** Чем определяется производительность процессорного ядра микроконтроллера?

- 7. Какие вы знаете принципы построения процессоров?

- 8. В чём отличие гарвардской (фон Неймана) архитектуры от принстонской?

- 9. Что такое напряжение хранения информации?

- 10. Какие вы знаете группы регистров микроконтроллера?

- 11. Что такое порт микроконтроллера и зачем он нужен? Какие бывают порты?

- **12.** Какие могут быть источники внутренних запросов прерываний микроконтроллера?

- 13. Какие вы знаете режимы работы микроконтроллера?

- 14. Какие вы знаете режимы пониженного электропотребления?

### Лекция 8

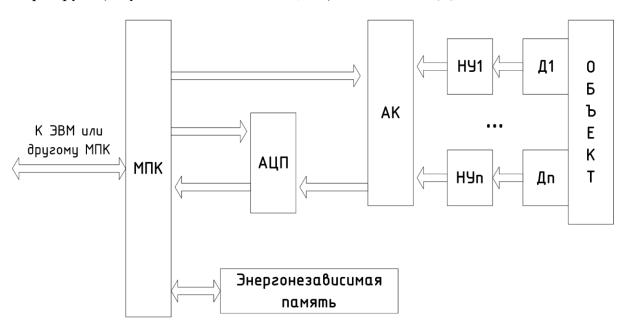

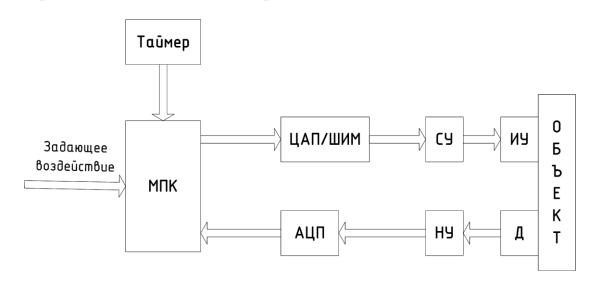

### Промежуточный контроль