# mov call MOV xor mov mov lea inc mov call inc mov xor mov lea inc call lea xor push lea mov mov inc mov mov call lea

mov

add

lea

esp, OCh

edx, [ebp+var 194]

mov

[ecx]

eax, [eax+2D8h]

dword ptr [ebx+1Ch]

sub 469338

eax, [eax]

eax,

word ptr [ebx+10h], 254h

, ecx, ecx

edx, offset algnore 1; "Ignore"

[ebp+var 10], ecx

eax, [ebp+var 188]

dword ptr [ebx+10h]

word ptr [ebx+10h], 8

sub 4B23D8

edx, edx

[ebp+var\_18C], edx

edx, [ebp+var\_18C]

dword ptr [ebx+1Ch]

sub\_49B5B8

eax, [ebp+var\_18C]

ecx, ecx

eax

edx, [ebp+var\_180]

word ptr [ebx+10h], 260h

PPULEUPH.

# ИВМ

dword ptr [ebx+1Ch] dec [ebp+var 18C] lea edx, 2 mov sub 4B2538 call dec dword ptr [ebx+1Ch] [ebp+var 188] lea eax, edx, 2 mov call sub 4B2538 dword ptr [ebx+1Ch] dec lea eax, [ebp+var 184] edx, 2 mov call sub 4B2538 dec dword ptr [ebx+1Ch] [ebp+var 180] lea eax, edx, 2 mov call sub 4B2538 pop eax al, al test loc 406E9A jz mov word ptr {e push offset alg edx, offset mov lea [ebp+var eax, call sub 4B23D8 dword ptr [ebx+1Ch] inc [ebp+var 194] lea edx, mov [eax] ecx, xor eax, eax push ecx [ebp+var 194], eax mov push edx dword ptr [ebx+1Ch] inc call sub 409BA0

# БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ФАКУЛЬТЕТ РАДИОФИЗИКИ И ЭЛЕКТРОНИКИ Кафедра кибернетики

### И. А. Шалатонин

# микропроцессоры и пэвм

Конспект лекций

Для студентов II курса специальности: E 25 01 10 «Коммерческая деятельность на рынке радиоэлектронных средств и информационных услуг»

> Минск БГУ 2004

УДК 004.3(075.8) ББК 32.973я73 III18

### Рецензенты:

доктор технических наук, профессор А. А. Петровский; кандидат технических наук, доцент В. С. Садов

Печатается по решению Редакционно-издательского совета Белорусского государственного университета

### Шалатонин И. А.

Ш18 Микропроцессоры и ПЭВМ: Курс лекций / И. А. Шалатонин. – Мн.: БГУ, 2004. – 141 с. ISBN 985-485-177-X.

В курсе лекций рассматриваются основные типы архитектур и структур ПЭВМ, приведены описания основных типов универсальных микропроцессоров и микроконтроллеров ведущих зарубежных компаний. Проанализированы основные идеи построения микропроцессорных систем. Изложено современное состояние средств вычислительной техники, этапы разработки микропроцессорной системы.

Предназначено для студентов факультета радиофизики и электроники специальности Е 1-25 01 10 08 "Коммерческая деятельность на рынке радиоэлектронных средств и информационных услуг".

УДК 004.3(075.8) ББК 32.973я73

© Шалатонин И. А., 2004

© БГУ, 2004

# СОДЕРЖАНИЕ

| B  | ВЕДЕНИЕ. ОСНОВНЫЕ ТЕРМИНЫ И ОПРЕДЕЛЕНИЯ                     | 5  |

|----|-------------------------------------------------------------|----|

| 1. | КЛАССИФИКАЦИЯ АРХИТЕКТУР И СТРУКТУР<br>МП И ПЭВМ            | 7  |

|    | 1.1. Вычислительная машина Джона фон Неймана                |    |

|    | 1.2. Классификация архитектур ЭВМ по интегральным признакам | 9  |

|    | 1.2.1. Классификация архитектур по взаимодействию процес-   |    |

|    | сора, памяти и устройств ввода-вывода                       | 10 |

|    | 1.2.2. Классификация архитектур по взаимодействию потока    |    |

|    | команд и потока данных                                      | 14 |

| 2. | АРХИТЕКТУРА И СТРУКТУРА МП И МПС                            | 17 |

|    | 2.1. История создания МП                                    |    |

|    | 2.2. Компоненты архитектуры МП                              |    |

|    | 2.3. Архитектурные особенности современных микропроцессоров |    |

|    | 2.4. Структура рынка универсальных микропроцессоров         |    |

|    | 2.5. Кодовые наименования МП                                | 34 |

|    | 2.6. Структура микропроцессорной системы                    |    |

|    | 2.6.1. Программный ввод-вывод                               |    |

|    | 2.6.2. Ввод-вывод по прерываниям                            |    |

|    | 2.6.3. Ввод-вывод в режиме прямого доступа к памяти         |    |

|    | 2.6.4. Последовательный и параллельный ввод информации      | 43 |

| 3. | INTEL-СОВМЕСТИМЫЕ МИКРОПРОЦЕССОРЫ                           | 46 |

|    | 3.1. Процессоры фирмы Intel                                 | 46 |

|    | 3.2. Маркетинговая революция в Intel                        |    |

|    | 3.3. Процессоры фирмы AMD                                   | 69 |

|    | 3.4. Микропроцессоры компаний Cyrix, Centaur Technology и   |    |

|    | Transmeta                                                   | 74 |

| 4. | ПРОЦЕССОРЫ ФИРМЫ MOTOROLA                                   | 75 |

| 5. | УСТРОЙСТВО ПЕРСОНАЛЬНОГО КОМПЬЮТЕРА                         | 85 |

|    | 5.1. Состав типового компьютера                             |    |

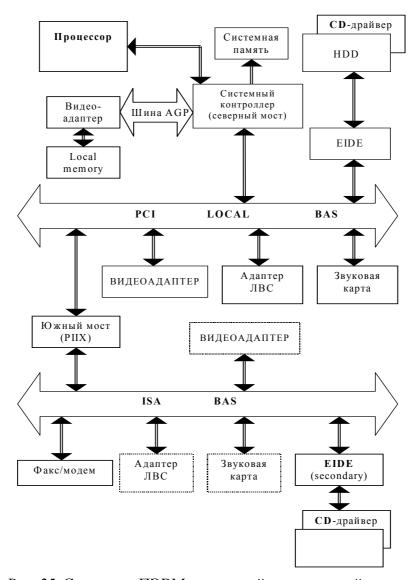

|    | 5.2. Структура персонального компьютера                     |    |

|    | 5.3. Материнские платы                                      |    |

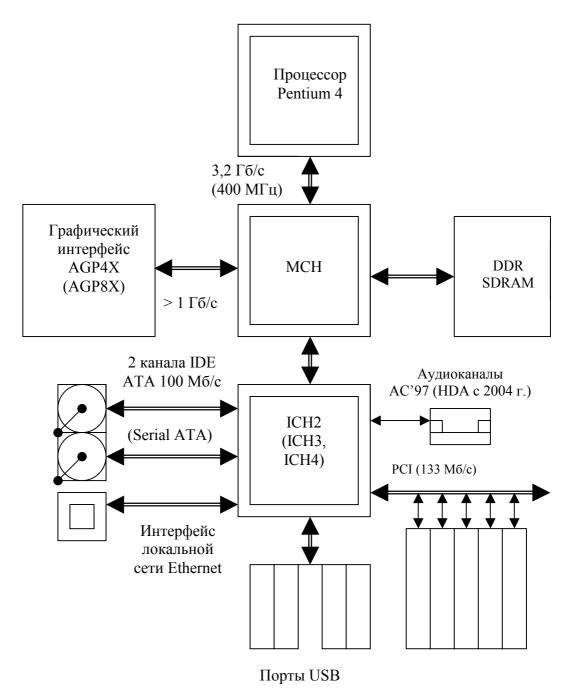

|    | 5.4. Чипсеты                                                |    |

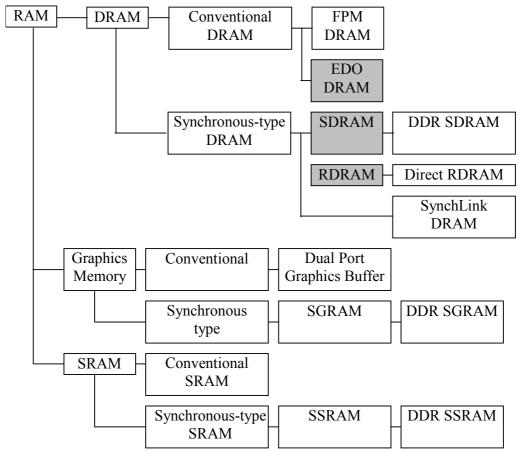

| 5.5. Память ПК                                      | 92  |

|-----------------------------------------------------|-----|

| 5.6. Интерфейсы современных ПК                      | 99  |

| 5.7. Накопители                                     |     |

| 5.8. Видеоадаптеры и мониторы                       | 110 |

| 6. ОЦЕНКА ПРОИЗВОДИТЕЛЬНОСТИ ПК                     | 115 |

| 7. ПРОИЗВОДИТЕЛИ BRAND-NAME ПК                      | 117 |

| 7.1. IBM PC и совместимые компьютеры                | 117 |

| 7.2. Персональные компьютеры от фирмы Apple         |     |

| 8. МИКРОКОНТРОЛЛЕРЫ                                 | 125 |

| 8.1. Архитектура и структура микроконтроллеров      | 125 |

| 8.2. 8-, 16-, 32-разрядные микроконтроллеры         | 130 |

| 8.3. Этапы проектирования микропроцессорной системы | 137 |

| ЛИТЕРАТУРА                                          | 141 |

# **ВВЕДЕНИЕ**

## ОСНОВНЫЕ ТЕРМИНЫ И ОПРЕДЕЛНИЯ

**Информатика** – это наука, которая изучает общие закономерности обработки информации с помощью ЭВМ. В информатике можно выделить три составные части: hardware (аппаратные средства), software (программные средства), brainware (теоретические методы решения задач: brain – мозг, умственная способность).

**ПЭВМ** (PC – Personal Computer) – это электронное устройство, осуществляющее прием, обработку, хранение, выдачу информации в соответствии с командами пользователя.

Следует отметить, что термин "компьютер" устойчиво заменил более длинное слово "электронная вычислительная машина" и аббревиатуру ПЭВМ.

Одним из крупнейших достижений интегральной электроники явилось появление в начале 70-х годов микропроцессоров (МП).

**Микропроцессором (МП)** называется программно-управляемое устройство, осуществляющее прием, обработку и выдачу цифровой информации, построенное на основе одной или нескольких больших интегральных схем (БИС). МП нельзя рассматривать как результат революционного открытия. Это скорее естественный этап в эволюции микроэлектронной технологии.

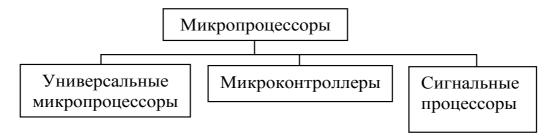

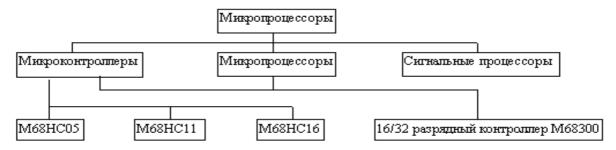

В процессе более чем 30-летнего развития произошла дифференциация микропроцессоров по функционально-структурным особенностям и областям применения. В настоящее время имеются следующие основные классы микропроцессоров (рис. 1): универсальные микропроцессоры; микроконтроллеры; сигнальные процессоры.

Рис. 1. Основные классы микропроцессоров

Универсальные микропроцессоры предназначаются для применения во всех типах вычислительных устройств: персональных ЭВМ, рабочих станциях, а в последнее время и в массово-параллельных супер-ЭВМ. Кроме того, универсальные микропроцессоры используются в телекоммуникационном оборудовании, системах автоматического управления и встроенной промышленной автоматике. Основной характеристикой этих микропроцессоров является наличие развитых устройств для эффективной реализации операций с плавающей точкой над 32- и 64-разрядными и более длинными операндами. В последнее время в состав этих микропроцессоров включаются функциональные блоки для обработки мультимедийной информации.

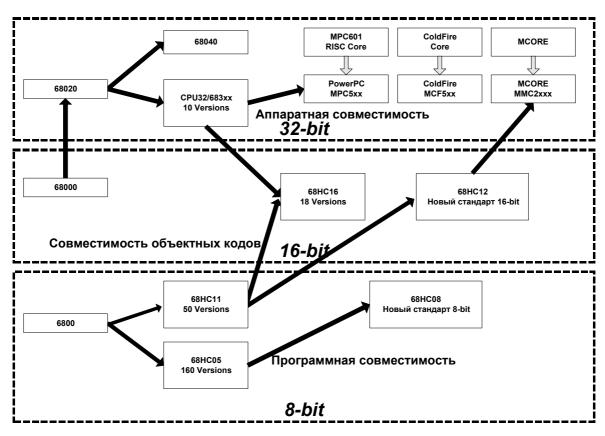

Микроконтроллер (МК, MCU – MicroController Unit) – это микропроцессорное устройство, специализированное на выполнение определенных функций управления, регулирования, идентификации. От обычного микропроцессора он отличается наличием встречных таймеров, счетчиков, ПЗУ, ОЗУ, схем сравнения, аналого-цифрового преобразования, последовательной связи и т. д. Общее число типов кристаллов МК с различными системами команд превышает 500, и все они, в силу существования изделий с их использованием, занимают свою устойчивую долю рынка. Лидером в производстве микроконтроллеров является фирма Motorola (около 15 % общемирового выпуска), в числе ведущих производителей этих изделий находятся также фирмы NEC, Mitsubishi, Hitachi, Intel, Texas Instruments, Philips, Atmel, ST – Microelektronics, Microchip.

Сигнальные процессоры (Digital Signal Processor (DSP), цифровой процессор обработки сигналов (ЦПОС))— относятся к классу специализированных микропроцессоров, ориентированных на выполнение алгоритмов цифровой обработки сигналов (ЦОС) в реальном времени. Это обусловливает их сравнительно малую разрядность и преимущественно целочисленную обработку. Однако современные сигнальные процессоры способны проводить вычисления с плавающей точкой над 40-разрядными операндами.

Основными производителями DSP являются фирмы Texas Insruments, Analog Devices, Motorola, NEC.

В курсе лекций будут рассмотрены универсальные процессоры и микроконтроллеры. Изучению ЦПОС будут посвящены соответствующие дисциплины.

# 1. КЛАССИФИКАЦИЯ АРХИТЕКТУР И СТРУКТУР МП И ПЭВМ

**Архитектура** — это совокупность возможностей, предоставляемых МП или ПЭВМ пользователю, работающему на уровне машинных команд. В первом приближении можно сказать, что архитектура микропроцессора — это набор его команд. Под **структурой** будем понимать совокупность блоков устройства и связей между ними.

Термин "архитектура ЭВМ" был введен в начале 60-х годов одной из групп специалистов фирмы IВМ, работающей над реализацией проекта ЭВМ семейства IВМ-360. Этот термин предназначался для описания общей программной модели семейства IВМ-360 на уровне языка ассемблера. В соответствии с понятием архитектура модели ЭВМ могут иметь одну и ту же архитектуру, но отличаться схемной реализацией.

# 1.1. Вычислительная машина Джона фон Неймана

Общепринятая сегодня архитектура компьютеров не менялась с 1946 года, т. е. в течение примерно 50 лет.

В начале 40-х годов практически все разработки компьютеров выполнялись на базе электромеханических реле. Первой подобной разработкой был небольшой компьютер на основе нескольких электромеханических реле, выполненный немецким инженером Конрадом Цузе. Но изза войны работы Цузе не были опубликованы. В США в 1943 году на одном из предприятий фирмы IBM американец Говард Эйкен создал более мощный компьютер под названием "Марк-1". В качестве устройства ввода-вывода в компьютере использовались перфокарты. Компьютер уже позволял проводить вычисления в сотни раз быстрее, чем вручную (с помощью арифмометра), и реально использовался для военных расчетов. Однако электромеханические реле работали весьма медленно и недостаточно надежно. Поэтому, начиная с 1943 года, в США группа специалистов под руководством Джона Мочли и Преспера Эккерта начала конструировать компьютер ENIAC на основе электронных ламп. Созданный ими компьютер работал в тысячу раз быстрее, чем "Марк-1". Однако обнаружилось, что большую часть времени этот компьютер простаивал – ведь для задания метода расчетов (программы) в этом компьютере приходилось в течение нескольких часов или даже нескольких дней подсоединять нужным образом провода. А сам расчет после этого мог занять всего лишь несколько минут или даже секунд. Чтобы упростить и ускорить процесс задания программ, Мочли и Эккерт стали конструировать новый компьютер, который мог бы хранить программу в своей памяти. В 1945 году к работе был привлечен талантливый венгерский математик и физик Джон фон Нейман. Основные архитектурно-функциональные принципы построения ЦВМ были разработаны и опубликованы в 1946 году Джоном фон Нейманом и его коллегами Г. Голдстайном и А. Берксом в ставшем классическим отчете "Предварительное обсуждение логического конструирования электронного вычислительного устройства".

Вот эти основные принципы:

- Программное управление работой ЦВМ.

- Принцип условного перехода.

- Принцип хранимой программы.

- Принцип использования двоичной системы счисления для представления информации в ЭВМ.

- Принцип иерархичности ЗУ.

Эти принципы Джона фон Неймана показались вначале простыми и очевидными. К ним долго еще не относились как к фундаментальным положениям, определившим на многие годы бурное развитие цифровой вычислительной техники и кибернетики (что называют иногда второй промышленной революцией).

До этого времени вычислительные машины могли выполнять только команды, поступающие извне, например, с пульта оператора, перфоленты. Иногда при этом подключении проводки к электрическому табло установка системы переключателей и их настройка для решения всего одной задачи занимали целый рабочий день. А для перенастройки машины на решение новой задачи операторам приходилось проделывать всю работу заново.

В противоположность этому у современных компьютеров, работающих в соответствии с фоннеймановскими принципами, операторпрограммист вводит команды и данные в закодированном виде обычно с клавиатуры, магнитных дисков и других устройств ввода-вывода в память ЭВМ.

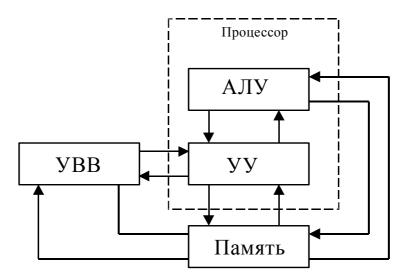

Эти основные идеи определяют и структуру ЭВМ фоннеймановского типа, в состав которой входят четыре основных блока: устройство управления (УУ), арифметико-логическое устройство (АЛУ), память, устройство ввода-вывода (рис. 2). Из рис. 2 следует еще одно определение процессора: УУ + АЛУ = Процессор.

Рис. 2. Структура ЭВМ фоннеймановского типа

Условно ЭВМ, работающая в соответствии с фоннеймановскими принципами, изображена на рис. 3.

Рис. 3. Структура типа ОКОД (SISD)

Таким образом, в архитектуре фон Неймана процесс обработки информации заключается в выполнении последовательности команд программы, написанной программистом. При этом команды должны выполняться именно в заданной последовательности (управление от потока команд). Сокращенно будем называть этот тип архитектуры ОКОД (Одиночный поток команд и данных) или SISD (Single instruction single Data).

В машинах, построенных на базе традиционной фоннеймановской архитектуры, обязательно присутствует программный счетчик (PC program counter).

# 1.2. Классификация архитектур ЭВМ по интегральным признакам

Дополним понятие архитектуры ЭВМ двумя новыми признаками:

1) Характер информационных связей между процессором, периферией и памятью.

2) Взаимодействие и структура потока команд и потока данных ввода-вывода.

# 1.2.1. Классификация архитектур по взаимодействию процессора, памяти и устройств ввода-вывода

Многообразие ПЭВМ в зависимости от характера связей процессора, памяти и устройств ввода-вывода можно свести к двум структурам:

- 1. С использованием каналов ввода-вывода.

- 2. Магистральная структура.

Особенность первого варианта — непосредственная связь ЦП и ОЗУ. Связь же с внешними устройствами осуществляется посредством специальных процессоров ввода-вывода, называемых часто каналами ввода-вывода (рис. 4). Использование нескольких каналов обеспечивает параллельное выполнение операций ввода-вывода с несколькими устройствами ввода-вывода.

Рис. 4. Структура ЭВМ с каналами ввода-вывода

Концепция магистральной структуры представлена на рис. 5.

Рис. 5. Магистральная структура ЭВМ

В этом случае все функциональные блоки ЭВМ единым образом подключены к единой системной магистрали.

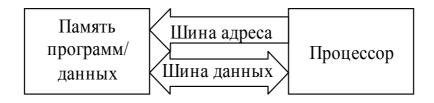

Гарвардская и принстонская архитектуры. Много лет назад правительство Соединенных Штатов дало задание Гарвардскому и Принстонскому университетам разработать архитектуру компьютера для военно-морской артиллерии. Принстонский университет разработал компьютер, который имел общую память для хранения программ и данных. Такая архитектура компьютеров больше известна как архитектура фон Неймана по имени научного руководителя этой разработки (рис. 6).

*Рис. 6.* Структура компьютера с архитектурой фон Неймана (принстонская архитектура)

Машины фон Неймана хранят программу и данные в одной и той же области памяти. В машинах этого типа команды содержат указание, что выполнить, и адрес данных, подлежащих обработке. Может показаться, что блок интерфейса в процессоре в этом случае является наиболее узким местом, так как одновременно с данными требуется выбирать из памяти очередную команду. Однако во многих процессорах с принстонской архитектурой эта проблема решается путем выборки следующей команды во время выполнения предыдущей. Такая операция называется предварительной выборкой (предвыборка), и она реализуется в большинстве процессоров с такой архитектурой. Данная архитектура обладает рядом положительных черт. Она является более дешевой, требует меньшего количества выводов шины.

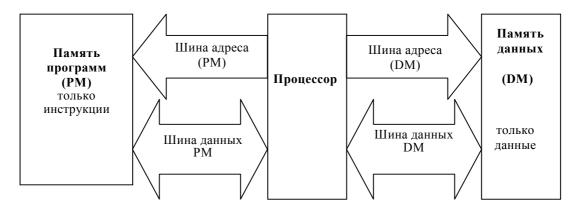

Гарвардский университет представил разработку компьютера, в котором для хранения программ и данных использовались отдельные банки памяти (рис. 7). Гарвардская архитектура имеет две физически разделенные шины данных. Это позволяет осуществить два доступа к памяти одновременно. Подлинная гарвардская архитектура выделяет одну шину для выборки инструкций (шина адреса PM – Program Memory), а другую для выборки операндов (шина данных DM – Data Memory).

Рис. 7. Структура компьютера с гарвардской архитектурой

Принстонская архитектура выиграла соревнование, так как она больше соответствовала уровню технологии того времени. Использование общей памяти оказалось более предпочтительным из-за ненадежности ламповой электроники (это было до широкого распространения транзисторов) — при этом возникало меньше отказов.

Гарвардская архитектура почти не использовалась до конца 70-х годов, когда производители микропроцессоров поняли, что эта архитектура дает преимущества устройствам, которые они разрабатывали. В архитектуре МК и ЦПОС многих фирм применен именно гарвардский принцип организации памяти, для которого характерно использование раздельной памяти программ и данных со своими шинами адресов и данных (рис. 7, 8).

| Внешняя<br>память<br>данны х | Память пр | Память программ |  | Внутренняя память<br>данны х |                                                 |  |

|------------------------------|-----------|-----------------|--|------------------------------|-------------------------------------------------|--|

|                              | внеш няя  |                 |  | косвенная                    | прямая                                          |  |

| 64 K                         | 64 К      | внутрен-        |  | 128<br>байтов                | SFR<br>ACC, B<br>SP, DPTR<br>P0, P1,<br>P2, P3, |  |

|                              |           | няя             |  |                              |                                                 |  |

|                              | 4 К       | 4 К             |  | 128 байто<br>R1, R2, R       | в R6, R7,<br>3, R4, R5                          |  |

*Рис.* 8. Особенности структуры памяти микроконтроллеров с гарвардской архитектурой (структура памяти соответствует МК MCS 51)

Основным преимуществом архитектуры фон Неймана (принстонской архитектуры) является то, что она упрощает устройство микропроцессора, так как реализует обращение только к одной общей памяти. Для микропроцессоров самым важным является то, что содержимое ОЗУ (RAM – Random Access Memory) может быть использовано как для хранения данных, так и для хранения программ. В некоторых приложениях программе необходимо иметь доступ к содержимому стека. Все это предоставляет большую гибкость для разработчика программного обеспечения, прежде всего в области операционных систем реального времени.

Гарвардская архитектура выполняет команды за меньшее количество тактов, чем архитектура фон Неймана. Это обусловлено тем, что в гарвардской архитектуре больше возможностей для реализации параллельных операций. Выборка следующей команды может происходить одновременно с выполнением предыдущей команды, и нет необходимости останавливать процессор на время выборки команды. В гарвардской архитектуре, обеспечивающей более высокую степень параллелизма операций, выполнение текущей операции может совмещаться с выборкой следующей команды.

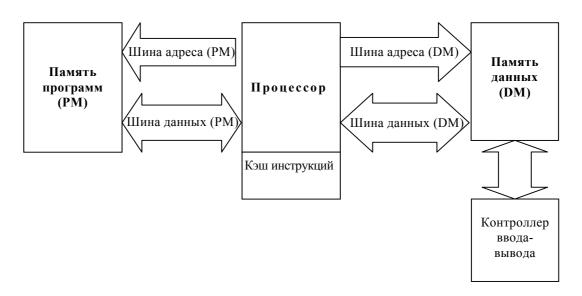

Важно отметить, что часто необходимо произвести выборку трех компонент – инструкции и двух операндов, на что, собственно, гарвардская архитектура не способна. В таком случае данная архитектура включает в себя кэш-память. Она может быть использована для хранения тех инструкций, которые будут использоваться вновь. При использовании кэш-памяти шина адреса (РМ) и шина данных (DM) остаются свободными, что делает возможным выборку двух операндов. Такое расширение – гарвардская архитектура плюс кэш – называют расширенной гарвардской архитектурой, или SHARC (Super Harvard ARChitecture). Эта архитектура предпочтительна для приложений, требующих больших объемов математических вычислений, например, таких, как БПФ и КИХфильтрация, используемых при обработке звука и речи и обеспеченных развитыми программными средствами и коммуникационными возможностями при построении параллельных многопроцессорных систем. Расширенная гарвардская архитектура представлена на рис. 9.

### **ВЫВОДЫ**

1. Таким образом, в большинстве случаев в ПЭВМ и универсальных МП реализуется **принстонская** магистральная архитектура, т. е. архитектура с общей магистралью данных и магистралью адресов при обращении к командам и данным. При этом архитектурном решении осу-

ществляется последовательная выборка и передача адресов команд и самих команд, адресов данных и самих данных по общей системе информационных магистралей — магистрали адреса, магистрали данных (МА, МД).

- 2. В микроконтроллерах (MCU) и цифровых процессорах обработки сигналов (DSP) чаще всего используется другая магистральная архитектура **гарвардская**, при которой реализуется раздельная память данных и программ, что позволяет увеличить загрузку МП.

- 3. Расширенная гарвардская архитектура SHARC (Super Harvard Architecture) предпочтительна для приложений, требующих больших объемов математических вычислений, например, таких, как БПФ и КИХфильтрация.

*Рис.* 9. Расширенная гарвардская архитектура микропроцессоров (SHARC)

# 1.2.2. Классификация архитектур по взаимодействию потока команд и потока данных

Предыдущая классификация охватывала взаимодействие трех основных групп устройств: память, ВУ, процессор.

В 1970 году, анализируя архитектуру ЭВМ, Г. Флинн выбрал основным определяющим архитектурным параметром взаимодействие потока команд и потока данных (операндов). В ЭВМ классической архитектуры ведется последовательная обработка данных. Команды поступают одна за другой (за исключением точек ветвления программы), и для них из ОЗУ или регистров также последовательно поступают операнды.

Одной команде (операции) соответствует один необходимый для нее набор операндов (как правило, два для бинарных операций). Архитектура этого типа, как мы уже знаем, называется ОКОД или SISD (рис. 10). Это классический фоннеймановский тип архитектуры.

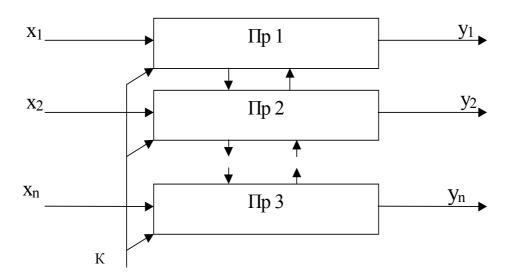

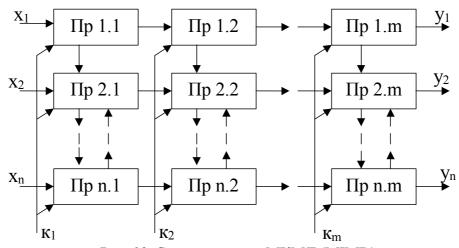

*Рис. 10.* Структура типа ОКМД (SIMD)

Тип ОКМД (Одиночный поток Команд и Множественный поток Данных) (SIMD - Single Instruction - Many Data). Охватывает такие системы, в которых одной командой обрабатывается набор из множества данных. Этот тип архитектуры используется, если задача легко делится на слабозависимые части и следует применять так называемую обработку, которая параллельную выполняется параллельно работающими процессорами. На рис. 10 изображена такая система из п взаимосвязанных процессоров (Пр), обрабатывающих п потоков данных  $x_1, x_2, ..., x_n$ , преобразуемых в n потоков результатов  $y_1, y_2, ..., y_n$ . Связи позволяют ИМ обмениваться необходимой процессорами промежуточной информацией. Такую систему обработки обозначают аббревиатурой ОКМД (Одиночный поток Команд и Множественный поток Данных). Одиночный поток команд называют потому, что каждый процессор выполняет одновременно только одну команду К (рис. 10). Эту схему обработки часто называют векторной, а мультипроцессор – векторным процессором. С его помощью очень удобно обрабатывать пмерные векторы, например траекторию движения летательного аппарата (в этом случае n = 3).

На этой основе строятся ассоциативные процессоры, специальные процессоры для обработки изображений и др. Число обрабатывающих

элементов может быть большим (порядка тысячи), но они работают синхронно над множеством данных.

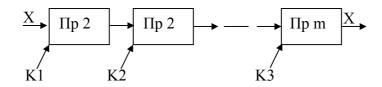

Структура типа MISD предназначена для обработки множественного потока команд и одиночного потока данных (МКОД): при обработке одного потока данных одновременно выполняется сразу несколько команд на разных процессорах. Такая схема получила название конвейерной обработки. Она очень удобна при работе с программами, которые нельзя разбить на полностью независимые части, но можно выделить фрагменты, связанные лишь через данные, которые обрабатывает программа.

Этот вид обработки похож на промышленный конвейер: роль рабочих мест играют процессоры, а заготовок — данные. Как и у промышленного конвейера, производительность конвейерной обработки определяется числом и трудоемкостью операций, выполняемых каждым процессором. Чем она меньше, тем быстрее работает конвейер (рис. 11).

Рис. 11. Структура типа МКОД (MISD)

Тип МКМД (МІМD— Many Instruction — Many Data) предусматривает наиболее полное и независимое распараллеливание процесса. Эта формула: МКМД — Множественный поток Команд и Множественный поток Данных — объединяет две предыдущие схемы (рис. 12). Такой мультипроцессор называют матричным, или векторно-конвейерным.

Рис. 12. Структура типа МКМД (МІМО)

# 2. АРХИТЕКТУРА И СТРУКТУРА МП И МПС

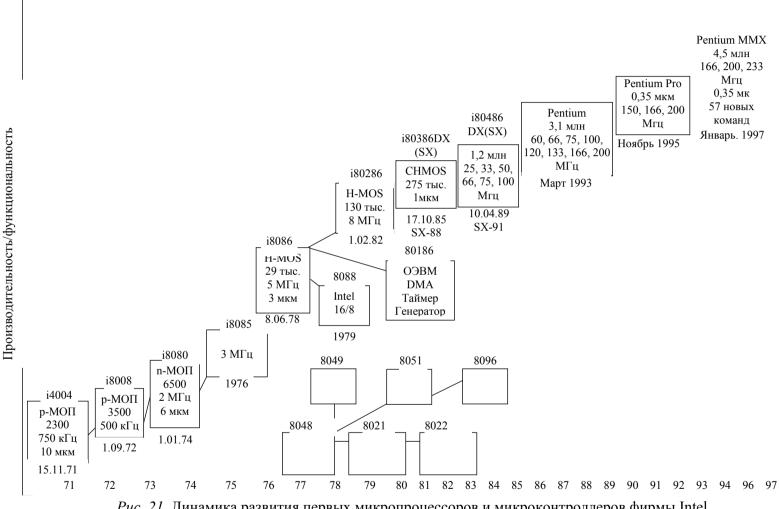

## 2.1. История создания МП

В 1969 г. фирма Intel (год основания фирмы – 1968) объявила о создании микросхемы, содержащей 1 Кбит памяти типа RAM (на тот момент эта память была самой емкой). Тогда еще не существовало других микрокомпьютерных чипов, к которым можно было подключить эту микросхему памяти.

Создание микропроцессора началось с малого: японская компания Busicom попросила Intel разработать микросхемы для мощных программируемых калькуляторов. Первоначально предполагалось, что будет создано двенадцать микросхем, но Тед Хофф из Intel предложил более интересное решение: одну универсальную микросхему, выбирающую команды из полупроводниковой памяти. Таким образом, полученное ядро могло справиться не только с требованиями Busicom, но и с множеством других задач.

Эта разработка оказалась настолько интересна, что Хоффу удалось убедить руководство компании выкупить права на нее у Busicom за \$ 60 тыс. и развить идею. В результате в конце 1971 года была представлена микросхема 4004 стоимостью \$ 200, содержащая 2800 транзисторов и обладающая вычислительной мощностью праотца компьютеров – ENIAC, который занимал целый дом и состоял из 18 000 ламп.

Термин "микропроцессор" впервые был употреблен в 1972 году, хотя годом рождения этого прибора следует считать 1971 год, когда фирма Intel выпустила микросхему серии 4004 – "интегральное микропрограммируемое вычислительное устройство".

Последующие поколения МП от корпорации Intel, представляющие собой 8-, 16-, 32- и 64-разрядные приборы, появились соответственно в 1972, 1978, 1985, 2000 г.

# 2.2. Компоненты архитектуры МП

Архитектура МП – это совокупность функциональных возможностей, доступных пользователю, работающему на уровне машинных команд. Другими словами, под архитектурой процессора понимается его представление с точки зрения программиста. Понятие архитектуры является комплексным и включает в себя:

1) структурную схему МП;

- 2) число и имена программно-доступных регистров (регистровая модель);

- 3) разрядность машинного слова;

- 4) систему команд;

- 5) формат команд;

- 6) доступный размер памяти V ( $V=2^n$ , где n- разрядность шины адреса);

- 7) режимы адресации памяти и внешних устройств;

- 8) организацию стека;

- 9) организацию прерываний (обработку нештатных ситуаций-исключений);

- 10) организацию интерфейса (interface сопрягать, согласовывать).

Разрабатывая программное обеспечение для МПС, программист должен знать архитектуру и технические характеристики МП.

Для облегчения анализа архитектурных особенностей современных процессоров, поясним следующие термины:

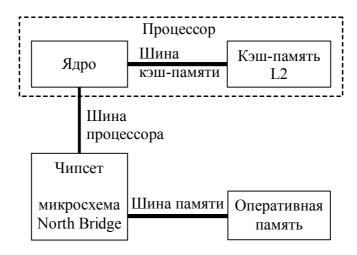

Тактовая частота ядра. В современных компьютерах процессор обменивается данными с внешними устройствами и памятью по системной шине с тактовой частотой, как правило, 66, 100, 133, 200 МГц. Вычислительное устройство процессора работает на более высоких частотах. Сначала материнская плата с помощью нескольких сигналов, подаваемых на вход процессора, выясняет, во сколько раз ядро процессора быстрее шины. После этого процессор самостоятельно начинает генерировать внутренний такт ядра.

Кэш-память первого уровня (L1) и второго уровня (L2). Все процессоры обладают встроенной промежуточной памятью, функционирующей с полной частотой ядра. С ее помощью ядро процессора может постоянно обращаться к данным, которые в течение короткого интервала времени используются многократно. Обычно предусматриваются два кэша; для программного кода и для данных. От их емкости непосредственно зависит производительность ЦП. Так, процессор Pentium MMX (P55C) работает быстрее своего предшественника Pentium, так как Intel вдвое расширила его кэш-память. Начиная с процессоров Pentium Pro и Pentium II, помимо L1-кэшей, имеется и дополнительный внутренний кэш второго промежуточного уровня (L2), функционирующий с частотой, превышающей частоту системной шины.

**Внутренняя гарвардская структура МП.** Разделение потока команд и данных с помощью введения отдельных блоков кэш-памяти пер-

вого уровня (L1) для хранения команд и данных, а также шин для их передачи.

Динамическое исполнение команд. Все микропроцессоры, начиная с Рептіит, располагали минимум двумя параллельно работающими блоками выполнения многочисленных операций – конвейерами, выполняющими программный код в несколько этапов. Если параллельно (суперскалярно) обрабатываются инструкции, не связанные друг с другом непосредственно, их результаты не обязательно получать одновременно (Out of Order Completion). Следовательно, один конвейер не должен простаивать в ожидании, пока другой не завершит выполнение команды (выполнение команд с опережением – спекулятивное выполнение).

**Предварительное исполнение команд**. В период, когда те или иные команды находятся в обработке, процессоры могут загружать и частично декодировать уже следующие программные инструкции. Если из-за ошибочного прогноза ветвления эта подготовительная работа окажется напрасной, процессору придется потратить значительное время на восстановление порядка. В связи с этим эффективность предварительного выполнения напрямую зависит от качества предсказания результатов ветвлений.

Буфер целевых адресов переходов (ВТВ). Чтобы команды ветвления, встречающиеся в программном коде, не слишком задерживали процесс его выполнения, МП пытается предсказать их результат без проверки тех или иных условий перехода. Для этого служит буфер целей переходов, в котором процессор запоминает цели последних встреченных переходов. Весьма вероятно, что один и тот же многократно выполненный условный переход (например, в цикле) будет иметь тот же целевой адрес и в следующий раз. Поэтому процессор заранее загружает код, считающийся предполагаемой целью перехода. В зависимости от размера ВТВ это предположение сбывается более или менее часто.

**Таблица предыстории ветвлений (ВНТ)**: в отличие от ВТВ ВНТ регистрирует лишь решения, принятые при выполнении последних операторов условных переходов, а не целевые адреса, которые процессор вынужден определять каждый раз заново, путем декодирования машинных команд.

# 2.3. Архитектурные особенности современных микропроцессоров

Анализ кода программ, генерируемого компиляторами языков высокого уровня, показал, что чаще всего используется только

ограниченный набор простых команд форматов "регистр, регистр  $\rightarrow$  регистр" и "регистр  $\leftrightarrow$  память". Компиляторы не в состоянии эффективно использовать сложные команды. Это наблюдение способствовало формированию концепции процессоров с сокращенным набором команд, так называемых RISC-процессоров (RISC – Reduced Instruction Set Computer).

Дейв Паттерсон и Карло Секуин сформулировали 4 основных принципа построения RISC-процессоров:

- 1. Любая операция должна выполняться за один такт, вне зависимости от ее типа.

- 2. Система команд должна содержать минимальное количество наиболее часто используемых простейших инструкций одинаковой длины.

- 3. Операции обработки данных реализуются только в формате "регистр ← регистр" (операнды выбираются из оперативных регистров процессора, и результат операции записывается также в регистр, а обмен между оперативными регистрами и памятью выполняется только с помощью команд загрузки/записи).

- 4. Состав системы команд должен быть "удобен" для компиляции операторов языков высокого уровня.

Таким образом, RISC-процессоры компьютеров с сокращенным набором команд имеют команды обработки типа "регистр  $\leftarrow$  регистр, регистр" и команды сохранения (store) и загрузки (load) типа "память  $\leftarrow$  регистр" и "регистр  $\leftarrow$  память" соответственно. Функциональные преобразования могут выполняться только над содержимым регистров, а результат помещается только в регистр.

После обособления RISC-процессоров в отдельный класс процессоры с традиционными наборами команд стали называться "CISC-процессорами" (CISC – Complicated Instruction Set Computer) с полным набором команд. Как правило, в этих процессорах команды имеют много разных форматов и требуют для своего представления различное число байтов памяти. Это обусловливает определение типа команды в ходе ее дешифрации при исполнении, что усложняет устройство управления процессора и препятствует повышению тактовой частоты до уровня, достижимого в RISC-процессорах на той же элементной базе.

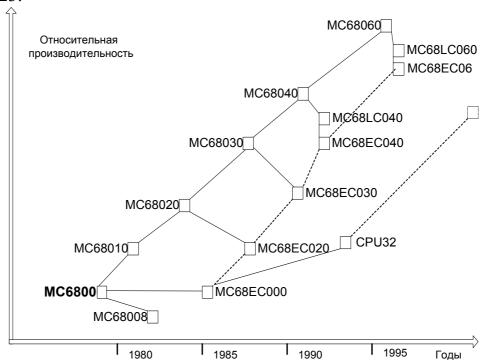

Микропроцессоры с классической CISC-архитектурой реализуют на уровне машинного языка комплексные наборы команд различной сложности (от простых, характерных для микропроцессора первого поколения, до сложных, характерных для 32-разрядных микропроцессоров типа 80486, 68040 и др.). Лидером в этой области является фирма Intel и

ее клонмейкеры, микропроцессорами которой комплектуется более 80 % выпускаемых персональных компьютеров. Микропроцессоры семейства М68ххх фирмы Motorola использовались в персональных компьютерах типа Macintosh. Микропроцессоры этого семейства широко применяются также в устройствах управления, встраиваемых в различные приборы и системы: контрольно-измерительную и связную аппаратуру, лазерные принтеры и контроллеры дисководов, роботы и системы промышленной автоматики.

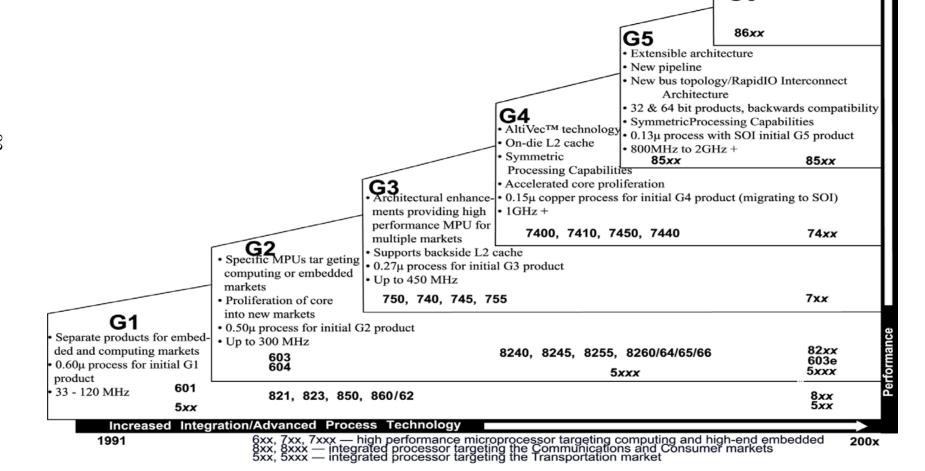

Микропроцессоры с RISC-архитектурой применяются, в основном, в рабочих станциях и мощных серверах. Широкое применение находят RISC-микропроцессоры семейств SPARC фирмы Sun Microsystems и RxOOO фирмы MIPS Computer Systems (с 1992 года является самостоятельным отделением Silicon Graphics). За последние годы очень активно внедряются в различную аппаратуру RISC-микропроцессоры семейства PowerPC – совместная разработка фирм IBM, Motorola и Apple Computers (альянс IMA). Процессоры PowerPC 7XX (G3), PowerPC 74XX (G4), PowerPC 970 (G5) являются основой построения персональных компьютеров іМас от фирмы Apple Computers. Среди фирм, выпускающих RISC-микропроцессоры, находятся также Intel, Hewlett-Packard, Digital Equipment. Необходимо также отметить транспьютеры – оригинальные RISC-микропроцессоры, разработанные фирмой Inmos для построения мультипроцессорных систем.

Развитие микропроцессоров происходит при постоянном стремлении сохранения преемственности программного обеспечения (ПО) и повышения производительности за счет совершенствования архитектуры и увеличения тактовой частоты. Сохранение преемственности ПО и повышение производительности, вообще говоря, противоречат друг другу. Так, например, процессоры с системой команд х86, относящиеся к классу CISC-процессоров вплоть до Pentium Pro, имели более низкие тактовые частоты по сравнению с микропроцессорами ведущих компаний производителей RISC-процессоров, изготавливаемых по одним и тем же технологическим нормам. Для этих процессоров существовали приложения, на которых производительность х86 микропроцессоров была значительно ниже, чем у RISC-процессоров, реализованных на той же элементной базе. Однако возможность использования совместимого программного обеспечения для различных поколений х86 процессоров обеспечивала им устойчивое доминирующее положение на рынке.

Затем на основе "пионерских" разработок компаний NexGen и AMD, позднее подхваченных компанией Intel, была реализована успешная попытка решения проблемы повышения производительности в рам-

ках архитектуры x86. Эти компании, сохраняя преемственность по системе команд с CISC-микропроцессорами семейства x86, создали новые устройства с использованием элементов RISC-архитектуры. Первыми примерами такого подхода могут служить микропроцессоры Nx586 (NexGen), K5, K6 (AMD), использующие концепцию RISC-ядра. В микропроцессор встраивается аппаратный транслятор, превращающий команды x86 в команды внутреннего RISC-процессора. Компания Intel впервые использовала этот подход в своих микропроцессорах с архитектурой P6.

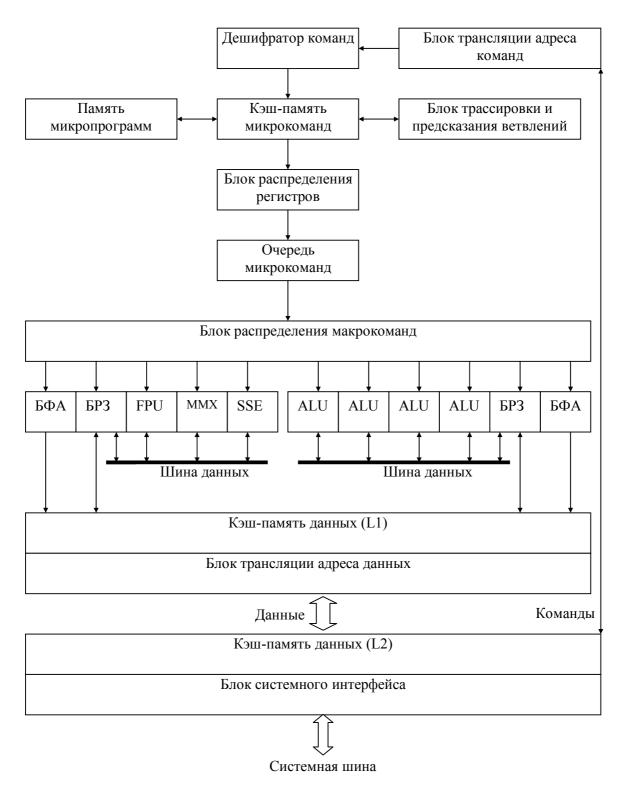

Важным элементом архитектуры, появившимся в МП i80486 фирмы Intel, стал конвейер — специальное устройство, реализующее такой метод обработки команд внутри микропроцессора, при котором исполнение команды разбивается на несколько этапов, i80486 имеет пятиступенчатый конвейер. Соответствующие пять этапов включают:

- выборку команды из кэш-памяти или оперативной памяти;

- декодирование команды;

- генерацию адреса, при которой определяются адреса операндов в памяти;

- выполнение операции с помощью АЛУ;

- запись результата (куда будет записан результат, зависит от алгоритма работы конкретной машинной команды).

Таким образом, на стадии выполнения каждая машинная команда как бы разбивается на элементарные операции. В чем преимущество такого подхода? Очередная команда после ее выборки попадает в блок декодирования. Таким образом, блок выборки свободен и может выбрать следующую команду. В результате на конвейере могут находиться в различной стадии выполнения пять команд. Скорость вычисления в результате существенно возрастает. Микропроцессоры, имеющие один конвейер, называются скалярными, а два и более — суперскалярными. Микропроцессор Pentium имеет два конвейера, то есть использует суперскалярную архитектуру, и поэтому может выполнять две команды за машинный такт. Внутренняя структура конвейера такая же, как и у і486. Микропроцессоры семейства Р6 (Pentium Pro/II/III) имеют другую структуру конвейера.

Современные микропроцессоры могут содержать десять и более конвейеров. В случае эффективной загрузки параллельно функционирующих устройств возможно получение в одном такте нескольких результатов операций, представленных скалярами: целочисленными операндами или операндами с плавающей точкой.

Эффективная загрузка параллельно функционирующих конвейеров обеспечивается либо аппаратурой процессора, либо компилятором, на входе которого поступают программы на традиционном последовательном языке программирования, либо совместно аппаратурой и компилятором. В компиляторах используется особая техника извлечения параллелизма из последовательных программ. Аппаратура микропроцессоров ориентирована на выделение более простых форм параллелизма, в том числе естественного.

Есть два крайних подхода к отображению присущего микропроцессору внутреннего параллелизма обработки данных на архитектурном уровне в системе команд.

**Первый подход** более консервативен и состоит в том, что никакого указания на параллельную обработку внутри процессора система команд не содержит. Именно такие процессоры относятся к классу суперскалярных. Такое название, с одной стороны, отличает эти процессоры от векторных процессоров, а с другой стороны, подчеркивает присущий этим процессорам внутренний параллелизм, обеспечивающий получение в одном такте нескольких скалярных результатов.

Второй подход, напротив, полностью открывает пользователю все возможности параллельной обработки. В специально отведенных полях команды каждому из параллельно работающих обрабатывающих устройств предписывается действие, которое устройство должно совершить. Такие процессоры называются процессорами с длинным командным словом (VLIW – Very Long Instruction Word). Предполагается, что существуют компиляторы с языков высокого уровня, которые готовят программы для загрузки их в микропроцессоры. Представители этой архитектуры: Crusoe от Transmeta, Itanium от Intel и российский Эльбрус 2000 (архитектура E2K).

Дальнейшее повышение производительности микропроцессоров связывается в настоящее время со статическим и динамическим анализом кода с целью выявления параллелизма уровня программных сегментов с использованием информации, предоставляемой компилятором языка высокого уровня. Исследования в данном направлении привели к разработке мультитредовой архитектуры процессоров, которые являются дальнейшим развитием суперскалярной архитектуры.

Суперскалярные микропроцессоры и микропроцессоры с длинным командным словом имеют один счетчик команд и в силу этого могут быть названы однотредовыми. В этих микропроцессорах команды, исследуемые на предмет возможности их параллельного совместного ис-

полнения, привязаны к счетчику команд процессора либо окном исполнения как в суперскалярных микропроцессорах, либо длинной командой как в микропроцессорах с длинным командным словом. Для того чтобы более агрессивно выбирать для параллельного исполнения команды одной или нескольких программ, в микропроцессор вводится несколько счетчиков команд. Микропроцессоры с несколькими счетчиками команд получили название мультитредовых. Уже появился первый мультитредовый микропроцессор фирмы Intel (старшие представители семейства Pentium 4 и процессоры Xeon). Мультитредовость в терминологии Intel получила название Hyper-Threading (гиперпоточность). Процессоры, в полной мере использующие все преимущества, предоставляемые мультитредовой архитектурой, разрабатываются фирмами IBM и SUN.

Суть технологии Hyper-Threading заключается в том, что в кристалл процессора добавлено несколько блоков, позволяющих одному физическому процессору распознаваться и работать в системе как два логических процессора, каждый из которых может быть загружен своей задачей. Основная часть блоков процессора используется совместно, но некоторые продублированы и могут выполнять разные задачи.

Технология Hyper-Threading помогает сократить периоды простоя процессора путем задействования ресурсов, не занятых одной задачей, исполнением инструкций другой задачи, например, в случае:

- задержек при доступе к памяти;

- выполнения последовательности взаимозависимых инструкций;

- ошибок предсказания ветвлений;

- одновременных вычислений в целочисленном и экспоненциальном форматах.

В результате пропускная способность основных ресурсов процессора возрастает, а суммарное время выполнения двух задач сокращается.

# 2.4. Структура рынка универсальных микропроцессоров

Доминирующее положение на рынке универсальных микропроцессоров занимают МП компании Intel и их клоны (микропроцессоры компаний AMD, VIA и др.) с системой команд **x86** (80 % рынка). Остальные производители универсальных микропроцессоров выпускают RISC-процессоры, суммарная доля которых составляет около 20 % рынка. Ар-

хитектура МП, выпущенных фирмой Intel, с системой команд х86 принято обозначать IA-32 (Intel Architecture -32).

В настоящее время на рынке присутствуют следующие микропроцессорные архитектуры, поддерживаемые соответствующими компаниями-разработчиками (указаны в скобках):

- Архитектура x86 (Intel, AMD, Cyrix, IDT, Transmeta);

- Архитектура IA-32 (Intel);

- Архитектура IA-64 (Intel);

- Архитектура Power PC (Motorola, IBM, Apple);

- Архитектура Power (IBM);

- Архитектура PA (Hewlett-Packard);

- Архитектура Alpha (Hewlett-Packard (DEC));

- Apxutektypa SPARC (SUN);

- Архитектура MIPS (MIPS).

Исторически микропроцессоры с архитектурой x86 доминировали в ПЭВМ, а RISC-процессоры использовались в рабочих станциях, высокопроизводительных серверах и суперкомпьютерах. В настоящее время процессоры с архитектурой x86 несколько потеснили RISC-процессоры в их традиционных областях применения, в то же время некоторые производители рабочих станций, например SUN, пытаются выйти со своими процессорами на рынок персональных ЭВМ.

На сегодняшний день основные производители микропроцессоров обладают примерно равными технологическими возможностями, поэтому в "борьбе за скорость" на первое место выходит фактор архитектуры. Архитектура микропроцессоров на протяжении ряда лет развивается по двум магистральным направлениям.

Первое направление получило условное название **Speed Daemon**. Оно характеризуется стремлением к достижению высокой производительности главным образом за счет высокой тактовой частоты при упрощенной внутренней структурной организации микропроцессора.

Второе направление – Brainiac – связано с достижением высокой производительности за счет усложнения логики планирования вычислений и внутренней структуры процессора. Каждое из направлений имеет собственных противников и сторонников и, по-видимому, право на существование.

В поисках способов достижения максимальной производительности разработчики микропроцессоров с RISC-архитектурой все чаще позволяют себе отходить от ее канонических принципов. В то же время в

микропроцессорах CISC-архитектуры, яркими представителями которых является семейство x86, внедряются решения, наработанные при создании RISC-процессоров.

**Архитектура микропроцессора IA-32.** История архитектуры IA-32 насчитывает уже более 15 лет. Эта архитектура является общей для всех 32-разрядных микропроцессоров Intel, начиная с i386. В табл. 1 приведены основные модели процессоров, в которых используется эта архитектура, и некоторые их характеристики.

$\it Taблица~1.$  Некоторые характеристики процессоров архитектуры IA-32

| Модель, начало вы-<br>пуска                             | Число тран-<br>зисторов | Тактовая час-<br>тота, МГц | Объем внутренней кэш-памяти (L1)                                            |

|---------------------------------------------------------|-------------------------|----------------------------|-----------------------------------------------------------------------------|

| i386,<br>октябрь 1985 г.                                | 275 тыс.                | до 40                      | Нет                                                                         |

| i486,<br>апрель 1989 г.                                 | 1,2 млн                 | до 100                     | 8 Кбайт – команды<br>8 Кбайт – данные                                       |

| Pentium,<br>март 1993 г.                                | 3,1 млн до 200          |                            | 8 Кбайт – команды<br>8 Кбайт – данные                                       |

| Pentium Pro,<br>ноябрь 1995 г.                          | 5,5 млн                 | до 200                     | 8 Кбайт – команды<br>8 Кбайт – данные                                       |

| Pentium MMX,<br>январь 1997 г.                          | 4,5 млн                 | до 233                     | 16 Кбайт – команды<br>16 Кбайт – данные                                     |

| Pentium II,<br>май 1997 г.<br>(Хеоп, июнь 1998 г.)      | 7,5 млн                 | до 450                     | 16 Кбайт – команды<br>16 Кбайт – данные                                     |

| Celeron,<br>апрель 1998 г.                              |                         | от 300                     | 16 Кбайт – команды<br>16 Кбайт – данные                                     |

| Pentium III,<br>февраль 1999 г.<br>(Xeon, март 1999 г.) | 8,5 млн                 | до 1200<br>(до 700)        | 16 Кбайт – команды<br>16 Кбайт – данные                                     |

| Pentium 4,<br>ноябрь 2000 г.<br>(Foster, 2001 г.)       | от 42 млн               | от 1400<br>(от 2000)       | от 12 Кбайт – микрокоманды<br>8 Кбайт – данные<br>от 256 Кбайт – общий (L2) |

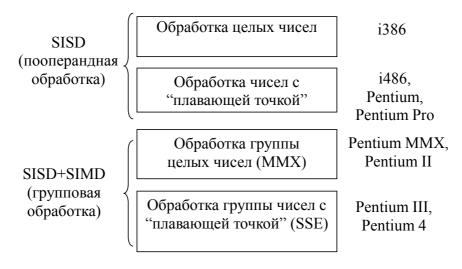

В процессе развития архитектуры IA-32 расширялись возможности обработки данных, представленных в различных форматах (рис. 13). Процессоры i386 выполняли обработку только целочисленных операндов.

Для обработки чисел с "плавающей точкой" использовался внешний сопроцессор i387, подключаемый к микропроцессору. В состав процессоров i486 и последующих моделей Pentium введен специальный блок FPU (Floating-Point Unit), выполняющий операции над числами с "пла-

вающей точкой". В процессорах Pentium MMX была впервые реализована групповая обработка нескольких целочисленных операндов разрядностью 1, 2, 4 или 8 байт с помощью одной команды. Такая обработка обеспечивается введением дополнительного блока MMX (Multi Media Extension – мультимедийное расширение). Название блока отражает его направленность на обработку видео- и аудиоданных, когда одновременное выполнение одной операции под несколькими операндами позволяет существенно повысить скорость обработки изображений и звуковых сигналов.

*Рис. 13.* Эволюция структуры AI-32

Начиная с модели Pentium III, в процессоры вводится блок SSE (Steaming SIMD Extension – потоковое SIMD-расширение) для групповой обработки чисел с "плавающей точкой".

Таким образом, если первые модели процессоров Pentium выполняли только пооперандную обработку данных по принципу "Одна команда – одни данные" (SISD – Single Instruction – Single Data), то, начиная с процессора Pentium MMX, реализуется также их групповая обработка по принципу "Одна команда – много данных" (SIMD – Single Instruction – Multiple Data). Соответственно расширяется и набор регистров процессора, используемых для промежуточного хранения данных (рис. 14). Кроме 32-разрядных регистров для хранения целочисленных операндов, процессоры Pentium содержат 80-разрядные регистры, которые обслуживают блоки FPU и MMX. При работе FPU регистры STO-ST7 образуют кольцевой стек, в котором хранятся числа с "плавающей точкой", представленные в формате с расширенной точностью (80 разрядов). При реализации MMX-операций они используются как

64-разрядные регистры ММО-ММ7, где могут храниться несколько операндов (восемь 8-разрядных, четыре 16-разрядных, два 32-разрядных или один 64-разрядный), над которыми одновременно выполняется поступившая в процессор команда (арифметическая, логическая, сдвиг и ряд других).

| 31            | 0_    | 79                    | 6463  | 0 | 127       | 0          |

|---------------|-------|-----------------------|-------|---|-----------|------------|

| EAX           | ST0   |                       | MM0   |   | XMI       | M0         |

| ECX           | ST1   |                       | MM1   |   | XMI       | M1         |

| EDX           | ST2   |                       | MM2   |   | XMI       | M2         |

| EBX           | ST3   |                       | MM3   |   | XMI       | М3         |

| EBP           | ST4   |                       | MM4   |   | XMI       | M4         |

| ESP           | ST5   |                       | MM5   |   | XMI       | M5         |

| ESI           | ST6   |                       | : MM6 |   | XMI       | М6         |

| EDI           | ST7   |                       | MM7   |   | XMI       | <b>М</b> 7 |

| Целочисленные |       | Регистры блоков       |       |   | Регистры  | ы блока    |

| регистры      | FPU ( | (ST0-7) и MMX (MM0-7) |       |   | SSE/SSE-2 | (XMM0-7)   |

Puc. 14. Регистры хранения данных в процессорах Pentium

Блок SSE-2, введенный в состав процессора Pentium 4, значительно расширяет возможности обработки нескольких операндов по принципу SIMD по сравнению с блоком SSE в модели Pentium III. Этот блок реализует 144 новые команды, обеспечивающие одновременное выполнение операций над несколькими операндами, которые располагаются в памяти и в 128-разрядных регистрах XMMO-XMM7. В регистрах могут храниться и одновременно обрабатываться 2 числа с "плавающей точкой" в формате двойной точности (64 разряда) или 4 числа в формате одинарной точности (32 разряда). Этот блок может также одновременно обрабатывать целочисленные операнды: шестнадцать 8-разрядных, восемь 16-разрядных, четыре 32-разрядных или два 64-разрядных. В результате производительность процессора Pentium 4 при выполнении таких операций оказывается вдвое выше, чем Pentium III.

Операции SSE-2 позволяют существенно повысить эффективность процессора при реализации трехмерной графики и интернет-приложений, обеспечении сжатия и кодирования аудио- и видеоданных и в ряде других применений.

Введение большой группы команд SSE-2 является основной особенностью реализованного в Pentium 4 варианта архитектуры IA-32. Что касается базового набора команд и используемых способов адресации операндов, то они практически полностью совпадают с набором команд и способов адресации в предыдущих моделях Pentium. Процессор обеспечивает реальный и защищенный режимы работы, реализует сегмент-

ную и страничную организации памяти. Таким образом, пользователь имеет дело с хорошо знакомым набором регистров и способов адресации, может работать с базовой системой команд и известными вариантами реализации прерываний и исключений, которые характерны для всех моделей семейства Pentium.

**Архитектура микропроцессора IA-64** реализует концепцию EPIC (Explicitly Parallel Instruction Computing – явное параллельное выполнение команд) и существенно отличается от архитектуры предыдущих, 32-разрядных микропроцессоров компании Intel.

Основными особенностями ЕРІС являются: большое количество регистров; масштабируемость по количеству функциональных устройств (возможность увеличения числа функциональных устройств в последующих моделях микропроцессора); явное задание параллелизма в машинном коде; предикатное исполнение инструкций; упреждающая загрузка данных по предположению.

Основные отличия архитектуры процессора IA-64 от архитектуры процессора x86 (IA-32) приведены ниже в табл. 2.

Таблица 2 Отличия архитектур процессоров x86 и IA-64

| Процессор х86 (ІА-32)                 | Процессор ІА-64                      |

|---------------------------------------|--------------------------------------|

| Использование сложных инструкций      | Использование простых инструкций,    |

| переменной длины, обрабатываемых по   | сгруппированных по три, одинаковой   |

| одной                                 | длины                                |

| Переупорядочивание и оптимизация ин-  | Переупорядочивание и оптимизация     |

| струкций во время выполнения          | инструкций во время компиляции       |

| Попытки предсказания переходов        | Исполнение нескольких последова-     |

|                                       | тельностей команд одновременно без   |

|                                       | предсказания переходов               |

| Загрузка данных из памяти по мере не- | Загрузка данных до того, как они по- |

| обходимости                           | требуются                            |

Архитектура IA-64 объединяет в себе лучшие качества суперскалярных микропроцессоров и микропроцессоров с длинным командным словом (VLIW-Very Long Instruction Words). Микропроцессор Itanium является первым представителем 64-разрядных микропроцессоров Intel. В микропроцессоре Itanium, как и в других микропроцессорах VLIW-архитектуры, последовательность команд и план загрузки исполнительных устройств формируются на этапе компиляции. В ходе выполнения программы последовательность команд не изменяется. В микропроцессоре используются: динамическое предсказание переходов, спекулятивное (по предположению) исполнение команд, аппаратная поддержка

конвейерного выполнения циклов, отложенные операции обращения к памяти, предварительная загрузка данных в кэш.

Архитектура Power (микропроцессоры Power 3, Power 4) разрабатывается компанией IBM с конца 1980-х годов. В ее основе лежат принципы RISC-архитектуры: фиксированный формат команд, регистровые операции, однотактовое выполнение команд, простые способы адресации, большой регистровый файл. В то же время имеется несколько существенных особенностей, отличающих данную архитектуру от архитектур других RISC-процессоров. К ним относятся: независимый набор регистров для каждого из исполнительных устройств; включение в систему отдельных CISC-подобных инструкций (например, команды групповой загрузки/сохранения, команды манипуляции битовыми полями, смешанные команды умножения-сложения с плавающей точкой); отсутствие механизма "задержанных переходов" (т. е. опережающее выполнение команды, следующей за командой условного перехода); оригинальный способ реализации условных переходов (наличие разряда условного выполнения в коде операции каждой команды и нескольких регистров условий). Основной областью применения микропроцессоров с архитектурой являются высокопроизводительные серверы и суперкомпьютеры.

**Архитектура PowerPC** появилась в результате стремления разработчиков применить созданную архитектуру Power и в менее производительных, дешевых системах для персональных компьютеров и рабочих станций начального уровня.

Первый микропроцессор с данной архитектурой (PowerPC 601) появился в 1991 году в результате совместных усилий трех компаний: автора архитектуры Power – IBM, одного из лидеров в производстве персональных компьютеров – Apple и производителя микропроцессоров для компьютеров Apple – Motorola.

В настоящее время архитектура PowerPC используется в микропроцессорах IBM и Motorola, применяемых в контроллерах, телекоммуникационном оборудовании, персональных компьютерах, серверах и рабочих станциях. В то же время IBM продолжает самостоятельно разрабатывать микропроцессоры с архитектурой Power, ориентированные на использование в высокопроизводительных мультипроцессорных системах.

В последних разработках Motorola и IBM новые архитектурные решения сочетаются с прогрессивной технологией производства микросхем (медные соединения, SOI), позволяющей уменьшить размер кристалла, снизить энергопотребление и поднять тактовую частоту микропроцессоров. К наиболее интересным разработкам последнего времени

относятся микропроцессоры, G3 (PowerPC 750/740), G4 (PowerPC 7400), G5 (PowerPC 970), Power 3, Power 4. Технология обработки мультимедийных данных AltiVec, предложенная компанией Motorola, впервые была реализована в микропроцессоре PowerPC G4. 64-разрядный микропроцессор Power3 разработан компанией IBM как альтернатива высокопроизводительным процессорам Intel и Alpha. Микропроцессор Power 4 имеет систему команд IBM ISA, реализованную в ЭВМ RS/6000 и AS/400 и полностью совместимую с системой команд PowerPC.

**Архитектура микропроцессоров Alpha** впервые была представлена в феврале 1992 года компанией DEC, а уже в феврале 1993 года был выпущен первый из микропроцессоров Alpha 21064 с тактовой частотой 200 МГц, выполненный по 0,75 мкм КМОП технологии с 4 слоями металлизации. Процессор содержал 1,68 млн транзисторов на кристалле площадью 238 мм<sup>2</sup>.

Благодаря высокой тактовой частоте и высокой степени конвейеризации выполняемых операций (до 10 тактов на операцию) этот микропроцессор надолго занял лидирующее положение по производительности. Основной областью использования процессора явились высокопроизводительные рабочие станции и серверы.

На протяжении ряда лет микропроцессоры Alpha, разработанные компанией DEC, являлись лидерами в производительности. Первые 64-рядные микропроцессоры разрабатывались в рамках концепции Spead Daemon, затем, начиная с модели 21264, разработчики начали использовать решения, характерные для концепции Brainiac.

Микропроцессор нового поколения Alpha 21264 был представлен в мае 1997 года. Микропроцессор содержал 15,2 млн транзисторов на кристалле площадью  $310~{\rm mm}^2$  и изготовлялся по КМОП-технологии с 6 слоями металлизации.

В отличие от предыдущих микропроцессоров семейства, наряду с высокой тактовой частотой, в Alpha 21264 использовался сложный механизм динамического исполнения команд: динамическое планирование с изменением последовательности команд, переименование регистров, спекулятивное выполнение команд.

Новый микропроцессор компании Hewlett-Packard Alpha 21364 (в 1998 год компания DEC, разработчик архитектуры микропроцессоров Alpha, была куплена Сотрад, которая в свою очередь влилась в Hewlett-Packard) был выпущен в конце 2002 года.

Процессор содержит то же самое ядро, что и Alpha 21264, однако имеет ряд существенных дополнений. В отличие от предыдущего про-

цессора на кристалле размещена 6-входовая множественно-ассоциативная кэш-память второго уровня объемом 1,75 Мбайт, восьмиканальный контроллер динамической памяти Direct Rambus и сетевой интерфейс памяти.

**Архитектур PA (Precision Architecture)** была впервые реализована в 32-разрядном микропроцессоре PA-RISC компании Hewlett-Packard (HP) в 1986 году. Последовательно развивая принципы RISC архитектуры, в 1996 году HP выпустила микропроцессор PA-8000, в котором в полной мере воплощены основные принципы динамического исполнения команд ("интеллектуального выполнения" – в терминах Hewlett-Packard).

Следующим микропроцессором семейства стал РА-8600, представленный НР в конце 1999 года. В микропроцессоре использованы новые алгоритмы работы с кэш-памятью (алгоритм замещения квази-LRU (Least Recently Used Removal — удаляются долго не используемые страницы памяти)). Для повышения надежности кэш-память реализована с механизмом обнаружения и исправления ошибок. Улучшен алгоритм предсказания переходов. Суперскалярное устройство вычислений в формате с плавающей точкой позволяет за один такт получать до 4 результатов, что обеспечивает производительность микропроцессора 2,2 Gflops на тактовой частоте 550 МГц.

В марте 2000 года был выпущен очередной микропроцессор семейства — РА-8700. Новый микропроцессор изготавливается по 0,18-микронной КМОП-технологии "кремний на изоляторе" (SOI — Silicon on Insulator) с семислойными медными соединениями, что позволило разместить на кристалле 2,25 Мбайт кэш-памяти первого уровня (кэш данных — 1,5 Мбайт, кэш команд — 750 Кбайт), использовать пониженное напряжение питания и повысить тактовую частоту до 800 МГц и выше. Производительность микропроцессора составила 3,2 млрд. операций в секунду.

Одна из последних разработок компании HP – микропроцессор PA-8800 (кодовое название Mako) – представляет собой двухпроцессорную систему на основе модифицированного ядра PA-8700, выполненную на одном кристалле и размещенную в одном картридже с кэш-памятью второго уровня объемом 32 Мбайт.

Системная шина Мако такая же, как в процессоре Intel McKinley: ширина 128 бит, частота 400 МГц, пропускная способность 6,4 Гбайт/с. Процессор производится по 0,13 мкм технологии, с медными соединениями, изолятором с низкой диэлектрической постоянной и изолированной подложкой (SOI).

В дальнейших планах НР предусматривается выпуск еще одного микропроцессора РА-8900, рассчитанного на тактовую частоту 1,2–1,3 ГГц, и совместная с Intel работа над микропроцессорами с архитектурой IA-64.

Архитектура SPARC была создана компанией Sun Microsystems в 1985 г. В частности, в архитектуру SPARC вошла предложенная в Беркли концепция "регистровых окон", упрощающая создание однопроходных компиляторов и существенно снижающая количество команд обращения к памяти по сравнению с другими реализациями RISC-архитектуры. Семейство микропроцессоров с архитектурой SPARC включает 32-разрядные микропроцессоры MicroSPARC, SuperSPARC, HiperSPARC и 64-разрядный микропроцессор UltraSPARC. Основной областью применения SPARC-процессоров являются высокопроизводительные рабочие станции, серверы и суперкомпьютеры.

**Микропроцессоры с архитектурой MIPS** компании MIPS (с 1992 года является самостоятельным отделением фирмы Silicon Graphics) применяются в игровых приставках, карманных компьютерах, высокопроизводительных серверах, рабочих станциях и являются хорошей иллюстрацией воплощения концепции "Brainiac" в архитектуре процессора.

Разработанный компанией MIPS Technology Inc 64-разрядный микропроцессор R10000 построен на базе предыдущих поколений RISC-процессоров (R2000, R3000, R4000 и R5000).

В основе этого микропроцессора лежит суперскалярная RISC-технология пятого поколения, реализованная ранее в ориентированном на суперЭВМ процессоре R8000. Однако, в отличие от многокристального R8000, оптимизированного для высокопроизводительных научных расчетов, R10000 представляет собой однокристальный процессор общего назначения для настольных ПК, рабочих станций и серверов. Он обеспечивает лучший, чем в R8000, баланс между целочисленными операциями и операциями с плавающей точкой, что делает его более подходящим для широкого класса приложений. R10000 проектировался так, чтобы его можно было с равным успехом применять в бытовых ПК с Windows NT, на рабочих станциях с UNIX или в многопроцессорных серверах баз данных.

R10000 содержит высокоскоростной (до 1,6 Гбайт/с) внутрикристальный интерфейс "процессор-шина", позволяющий объединять в многопроцессорной конфигурации до четырех процессоров без использования дополнительных интерфейсных схем.

Следующий микропроцессор — R12000 — по архитектуре немногим отличается от R10000:

- в R12000 в 4 раза возросла емкость таблицы предсказания переходов до 2048 строк;

- появилась кэш-память адресов перехода емкостью 32 строки;

- с 32 до 48 увеличено максимальное число инструкций, которые могут выполняться с нарушением порядка следования;

- улучшена работа с кэш-памятью второго уровня;

- увеличены длины конвейеров.

В 2001 году Silicon Graphics (SG) выпустила очередной микропроцессор семейства — R14000. Этот микропроцессор производится по 0,13-микронной медной технологии и работает на частоте 500 МГц. Существенных изменений по сравнению с R12000 архитектура микропроцессора не претерпела.

В планах SG – выпуск R16000 с частотой 600 МГц, R18000 с частой 800 МГц и ожидаемой пиковой производительностью 3,2 Gflops, а также R20000 с частотой 1 ГГц и пиковой производительностью 4 Gflops. После 2005 года SG планирует свернуть микропроцессорное производство и в дальнейшем использовать в своих серверах и рабочих станциях микропроцессоры Intel/HP с архитектурой IA-64.

# 2.5. Кодовые наименования МП

Кодовые наименования различным изделиям присваивают во всех крупных фирмах и во всех странах. Это намного удобнее, чем в служебных разговорах и переписке использовать длинные и неудобоваримые официальные наименования. Иногда внутрифирменные кодовые наименования становятся известны широким слоям пользователей, и в очень редких случаях они входят в повседневный обиход.

С кодовыми наименованиями процессоров за последние два-три года произошло невероятное – ими не только стали пользоваться в разговорах, но они вошли в официальные документы и маркировку процессоров. Ниже приводится ряд кодовых наименований некоторых процессоров.

Корпорация Intel применяет следующие кодовые наименования:

• Banias – кодовое наименование процессоров с модифицированной архитектурой Pentium III, предназначенных для серверных приложений;

- Cascades кодовое наименование процессоров Pentium III Xeon, в которых использовалась технология 0,18 мкм;

- Coppermine наименование ядра процессоров Pentium III, а также процессоров Celeron, начиная с тактовой частоты 533 МГц. Такие процессоры отличаются пониженным напряжением питания ядра от 1,5 В до 1,7 В. Установка на системную плату, не снабженную регулятором напряжения, приводит к выходу процессора из строя;

- Covington первые варианты процессоров Celeron (1998 год);

- Deschutes наименование ядра процессоров Pentium II, которые выпускались по технологии 0,25 мкм (1998 год);

- Dixon наименование ядра мобильных процессоров Pentium II;

- Gallatin наименование нового варианта ядра Foster;

- Foster наименование ядра и процессоров Pentium 4 для серверных приложений с архитектурой Willamette;

- Itanium торговая марка для 64-разрядных процессоров;

- Katmai наименование ядра процессоров Pentium III (1999 год);

- Klamath наименование ядра первых процессоров Pentium II (1997 год);

- Madison новый вариант ядра McKinley;

- McKinley наименование ядра и процессоров второго поколения с 64-разрядной архитектурой;

- Mendocino наименование ядра процессоров Celeron (1998 год). Такой тип ядра использовался до тактовой частоты 533 МГц;

- Merced предварительное наименование процессора с архитектурой IA-64, официальное наименование Itanium;

- Northwood наименование ядра процессоров Pentium 4, для которых используется технология 0,13 мкм;

- Pentium торговая марка процессоров с суперскалярной архитектурой, зарегистрирована корпорацией Intel, чтобы избежать возможности использования названия другими фирмами (под маркой "486" выпускали процессоры многие фирмы);

- Prestonia наименование ядра и процессоров Pentium 4, развитие процессоров Xeon с микроархитектурой NetBurst;

- Prescott наименование ядра процессоров Pentium 4, выполненного по 90-нм технологии с 1 Мбайт кэша второго уровня, усовершенствованной технологией НТ и новыми командами;

- Tejas последователь ядра Prescott, с той же архитектурой Netburst, будет обладать, согласно предварительным данным, увеличен-

ным кэшем L1 (24/32 Кб), поддержкой улучшенной версии технологии HyperThreading. Вслед за этим ядром появится Nehalem, который будет обладать принципиально новой архитектурой. По предварительным подсчетам, чипы с ядром Тејаѕ "стартуют" с частот от 4,4 ГГц. К тому времени Prescott достигнет 4,0–4,2 ГГЦ;

- Tanner кодовое наименование процессоров Pentium III Xeon;

- Tualatin наименование ядра и процессоров Pentium Ш, для которых используется технология 0,13 мкм и уменьшенное напряжение;

- Willamette наименование ядра первых процессоров Pentium 4, для которых используется технология 0,18 мкм.

**Корпорация AMD** применяет следующие кодовые наименования:

- Athlon x86 наименование процессоров седьмого поколения;

- Athlon 64, Athlon 64 FX наименование процессоров восьмого поколения;

- Barton процессор с ядром Thoroughbred, выполненный по улучшенной технологии;

- Duron дешевый вариант процессора Athlon;

- Hammer наименование 64-разрядных процессоров (в дальнейшем для продвижения на рынке корпорация AMD присвоила ему торговую марку Opteron;

- Morgan наименование ядра нового поколения процессоров Duron, выполненных на ядре Palomino;

- Palomino наименование ядра второго поколения процессоров Athlon:

- Thunderbird наименование ядра процессоров Athlon, в которых используется технология 0,18 мкм.

**Корпорация VIA** применяет следующие кодовые наименования (для совместных разработок фирм Cyrix, National Semiconductors, TSMC и VIA):

- Samuel наименование ядра и процессора аналогов Celeron;

- Ezra наименование ядра и процессора с тактовой частотой от 750 МГц; О Ezra-T наименование ядра и процессора, совместимого с процессором Tualatin.

**Корпорация Centaur** применяет кодовое наименование Winchip для процессоров – аналогов второго поколения процессоров Pentium и Celeron.

**Корпорация Сотра** применяет кодовое наименование Alpha для процессоров с архитектурой, отличной от семейства x86.

**Корпорация Transmeta** применяет кодовое наименование Crusoe для процессоров с архитектурой, отличной от семейства x86.

# 2.6. Структура микропроцессорной системы

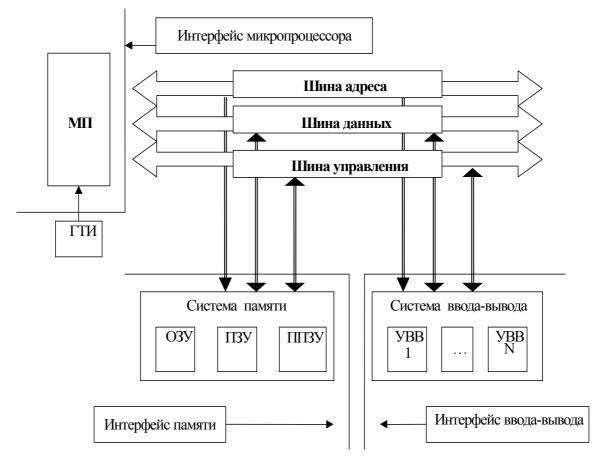

Микропроцессор всегда работает совместно с системой памяти (микросхемы ОЗУ, ПЗУ, ППЗУ), устройствами ввода-вывода (УВВ) информации (рис. 15). В памяти хранится программа решаемой задачи, исходные, промежуточные и окончательные результаты (данные), УВВ осуществляет ввод и вывод данных.

МП выполняет программу и управляет всеми перечисленными устройствами. Вычислительная система, представленная на рис. 15, называется **микропроцессорной системой** и реализуется на микропроцессорных БИС. Система построена по модульному принципу и имеет магистральную (шинную) организацию межмодульных связей.

Взаимодействие МП с памятью и УВВ требует выбора способа обращения к устройствам памяти и ввода-вывода, разработки системы адресации и внутреннего интерфейса МП-системы.

По способу организации взаимодействия устройств памяти и УВВ возможны два варианта организации системы:

- разделение адресов;

- выделение подсистемы.

При разделении адресов все элементы системы адресуются как ячейки памяти в том смысле, что для идентификации УВВ и устройств памяти не генерируется никаких специальных сигналов. Адрес, подаваемый на шину, дешифрируется памятью и системой ввода-вывода с целью определения его назначения, и в таких системах можно не использовать специальных команд ввода-вывода. Все поле адресов распределяется в этом случае между памятью и УВВ. Разделение адресов между памятью и УВВ достигается выделением одной (или нескольких) адресной линии для указания используемого устройства (память или ввод-вывод). Этот способ уменьшает в два (или более) раза емкость адресуемой памяти, поэтому может использоваться лишь в системах с небольшой емкостью памяти.

Использование одной (или более) адресной линии для идентификации устройств можно представить как перевод одной (или более) адресной линии в шину управления.

$Puc.\ 15.\$ Обобщенная структура МПС: **ГТИ** — генератор тактовых импульсов; **ПЗУ**, **ППЗУ** — перепрограммируемое запоминающее устройство; **ЗУ** — оперативное запоминающее устройство; **УВВ** — устройство ввода-вывода

В небольших МП-системах в дополнение к простоте адресации этот метод обеспечивает преимущества в использовании команд обращения к памяти вместо команд ввода-вывода. По командам ввода в МП-системах осуществляется просто загрузка требуемых данных в аккумулятор микропроцессора. Команды с обращением к памяти имеют более гибкие возможности по обработке данных.

При выделении подсистем вся МП-система разделяется на ряд подсистем (память, ввод, вывод, стек). В рамках каждой подсистемы используется вся совокупность адресов. Разделение всей системы на подсистемы осуществляется с помощью управляющих сигналов, которые появляются на специальных выводах микропроцессора. Обычно эти сигналы поддерживаются на выводах МП или шине данных в течение ограниченного интервала времени (в течение такта, например). Если необходимо запомнить и хранить слово состояния или управляющие сигналы

более длительное время, в состав МП-системы вводят специальный регистр – регистр состояния системы.

В архитектуре магистрального типа важное значение приобретает интерфейс. На рис. 15 показаны интерфейсы МП, системы памяти и системы ввода-вывода (ВВ). В узком смысле интерфейсом (от англ. Interfase — сопрягать, согласовать) называют устройство сопряжения; в широком смысле под интерфейсом понимают совокупность аппаратных, программных и конструктивных средств, обеспечивающих взаимодействие функциональных модулей системы.

Таким образом, для представленной на рис.15 микропроцессорной системы необходимым условием высокой эффективности использования является совместимость интерфейсов МП, системы памяти и системы ввода-вывода (ВВ). Работа рассматриваемой системы синхронизируется генератором тактовых импульсов (ГТИ).

Система работает с командами пересылки информации:  $M\Pi - \pi$  мять,  $M\Pi - \text{УВВ}$ , память – УВВ.

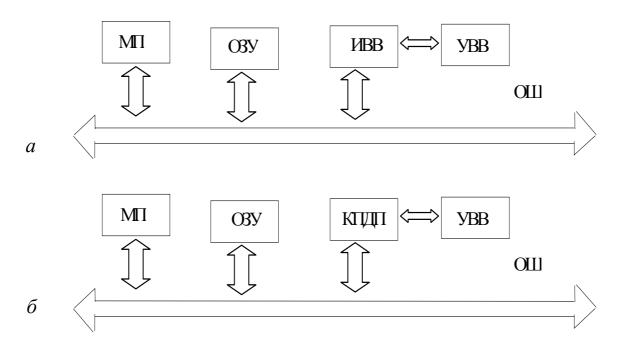

Для МП-системы разработано **три основных режима вводавывода:**

- программно-управляемый ввод-вывод,

- ввод-вывод по прерываниям,

- режим прямого доступа к памяти (ПДП).

#### 2.6.1. Программный ввод-вывод

Программный ввод-вывод — это наиболее простой способ обмена данными между процессором и внешним устройством. В этом случае всеми действиями по организации обмена управляет процессор, а всем другим элементам системы отводится пассивная роль сигнализации о своей готовности (асинхронный способ обмена). Непроизводительные потери времени МП на ожидание сигнала готовности от УВВ могут оказаться неприемлемыми для систем, работающих в реальном времени.

Известны два типа программно-управляемой передачи данных: синхронная, асинхронная.

Синхронная передача данных характерна для периферийных устройств, для которых известны временные соотношения. При этом типе передачи устройство ввода-вывода должно быть готово к приему или передаче данных за время, равное времени выполнения определенной команды процессора. Синхронная передача реализуется при минимальных затратах технических и программных средств.

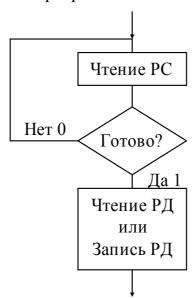

Асинхронная передача данных, иногда называемая обменом посредством "рукопожатия", широко используется в микроЭВМ. При такой передаче данных ЭВМ перед выполнением операции ввода-вывода проверяет состояние периферийного устройства. Блок-схема алгоритма асинхронного программного обмена (фрагмента некоторой программы) приведена на рис. 16.

Обычно при обмене необходимо:

- проверить состояние устройства (чтение регистра состояния (PC));

- активизировать устройство, если последнее готово к обмену;

- передать данные (чтение регистра данных (РД), запись РД);

- дезактивировать устройство.

Асинхронная передача является идеальной в смысле согласования временных различий между периферийными устройствами и процессором. Недостаток ее в том, что процессор вынужден ожидать, пока периферийное устройство не будет готово к обмену. Это приводит не только к непроизводительным затратам времени МП (при наличии длительных задержек), но и во многих случаях является просто недопустимым. Например, в процессах управления в этом случае возникает необходимость сохранения уровня сигналов управления на время ожидания передачи. Методом, позволяющим устранить подобные трудности, является передача данных с прерыванием программы.

Рис. 16. Блок-схема алгоритма асинхронного программного обмена

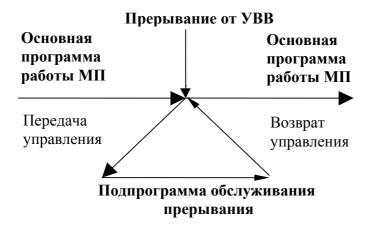

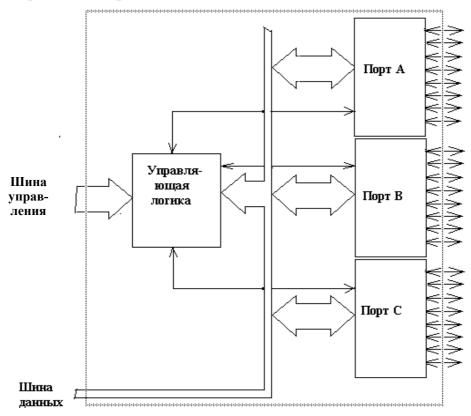

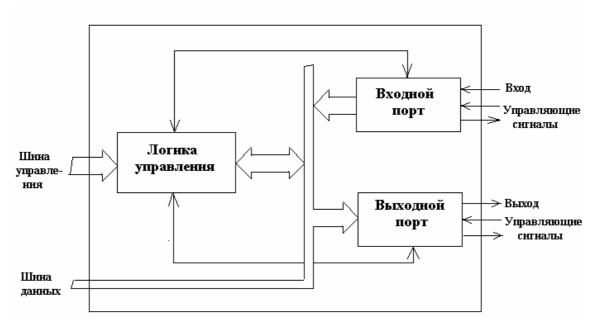

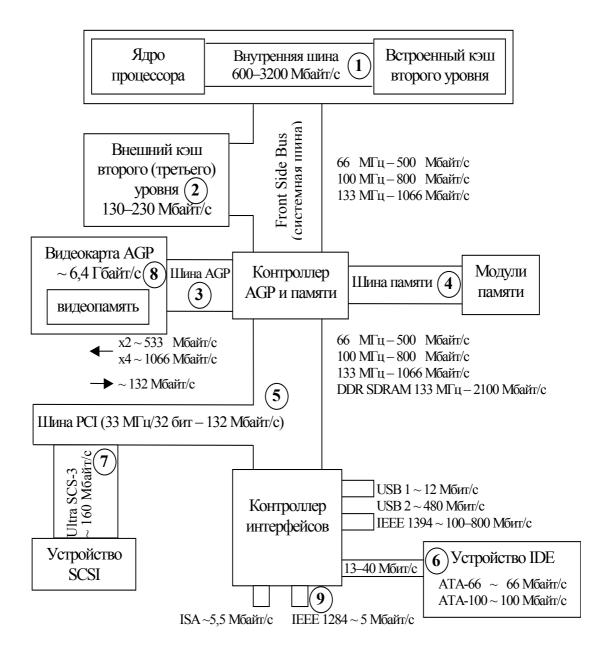

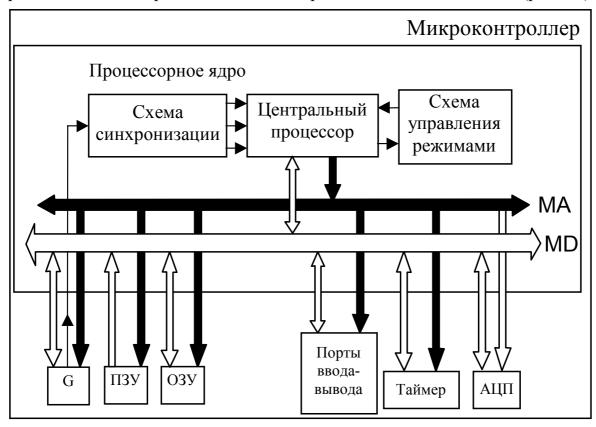

#### 2.6.2. Ввод-вывод по прерываниям