Application Specific Discretes A.S.D.™

### APPLICATIONS

Where transient overvoltage protection in ESD sensitive equipment is required, such as :

- Computers

- Printers

- Communication systems

- Cellular phone handsets and accessories

- Other telephone set

- Set top boxes

### FEATURES

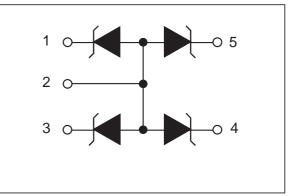

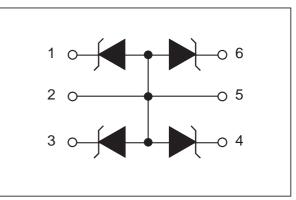

- 4 Unidirectional Transil<sup>™</sup> Functions

- Low leakage current: I<sub>R</sub> max. < 20 μA at V<sub>BR</sub>

- 500 W Peak pulse power (8/20 μs)

### DESCRIPTION

The ESDAxxSC5 and ESDAxxSC6 are monolithic voltage suppressors designed to protect components which are connected to data and transmission lines against ESD.

They clamp the voltage just above the logic level supply for positive transients, and to a diode drop below ground for negative transient.

### BENEFITS

High ESD protection level : up to 25 kV High integration Suitable for high density boards

### COMPLIES WITH THE FOLLOWING STAN-DARDS:

IEC61000-4-2 : level 4

15kV (air discharge) 8kV (contact discharge) MIL STD 883E-Method 3015-7 : class3B (human body model)

## ESDAxxSC5 ESDAxxSC6 QUAD TRANSIL ARRAY FOR ESD PROTECTION

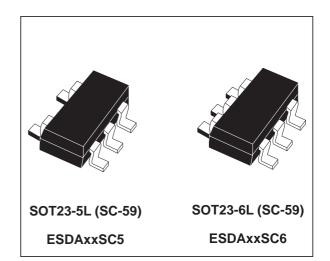

FUNCTIONAL DIAGRAM SOT23-5L

May 2002 Ed: 6F

| Symbol           | Test condition                                                             | Value                                              | Unit |   |

|------------------|----------------------------------------------------------------------------|----------------------------------------------------|------|---|

| V <sub>PP</sub>  | ESD discharge - MIL STD 883E - M<br>IEC61000-4-2 air o<br>IEC61000-4-2 con | 25                                                 | kV   |   |

| P <sub>PP</sub>  | Peak pulse power (8/20µs) note1                                            | ESDA5V3SCx<br>ESDA6V1SCx                           | 500  | W |

|                  |                                                                            | ESDA14V2SCx<br>ESDA17SC6<br>ESDA19SC6<br>ESDA25SC6 | 300  | W |

| Tj               | Junction temperature                                                       | 150                                                | °C   |   |

| T <sub>stg</sub> | Storage temperature range                                                  | -55 to +150                                        | °C   |   |

| TL               | Lead solder temperature (10 second of                                      | 260                                                | °C   |   |

| T <sub>op</sub>  | Operating temperature range                                                | -40 to +125                                        | °C   |   |

## **ABSOLUTE MAXIMUM RATINGS** (T<sub>amb</sub> = $25^{\circ}$ C)

### ELECTRICAL CHARACTERISTICS (Tamb = 25°C)

| Symbol          | Parameter                       |  |  |  |  |

|-----------------|---------------------------------|--|--|--|--|

| V <sub>RM</sub> | Stand-off voltage               |  |  |  |  |

| V <sub>BR</sub> | Breakdown voltage               |  |  |  |  |

| V <sub>CL</sub> | Clamping voltage                |  |  |  |  |

| I <sub>RM</sub> | Leakage current                 |  |  |  |  |

| I <sub>PP</sub> | Peak pulse current              |  |  |  |  |

| ατ              | Voltage temperature coefficient |  |  |  |  |

| С               | Capacitance                     |  |  |  |  |

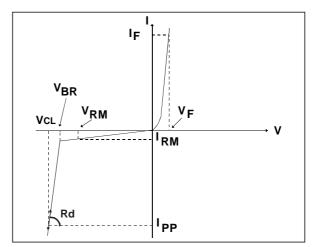

| Rd              | Dynamic resistance              |  |  |  |  |

| VF              | Forward voltage drop            |  |  |  |  |

|                            | V        | BR @     | <b>I</b> R | I <sub>RM</sub> @ | V <sub>RM</sub> | Rd         | αΤ                   | С        | V <sub>F</sub> @ | ₽ I <sub>F</sub> |

|----------------------------|----------|----------|------------|-------------------|-----------------|------------|----------------------|----------|------------------|------------------|

| Types                      | min.     | max.     |            | max.              |                 | typ.       | max.                 | typ.     | max.             |                  |

| Types                      |          |          |            |                   |                 | note 1     | note 2               | 0V bias  |                  |                  |

|                            | V        | V        | mA         | μΑ                | V               | mΩ         | 10 <sup>-4</sup> /°C | pF       | V                | mA               |

| ESDA5V3SC5<br>ESDA5V3SC6   | 5.3      | 5.9      | 1          | 2                 | 3               | 230        | 5                    | 280      | 1.25             | 200              |

| ESDA6V1SC5<br>ESDA6V1SC6   | 6.1      | 7.2      | 1          | 20                | 5.25            | 350        | 6                    | 190      | 1.25             | 200              |

| ESDA14V2SC5<br>ESDA14V2SC6 | 14.2     | 15.8     | 1          | 5                 | 12              | 650        | 10                   | 100      | 1.25             | 200              |

| ESDA17SC6<br>ESDA19SC6     | 17<br>19 | 19<br>21 | 1<br>1     | 0.075<br>0.1      | 14<br>15        | 700<br>800 | 10<br>8.5            | 85<br>80 | 1.2<br>1.2       | 10<br>10         |

| ESDA25SC6                  | 25       | 30       | 1          | 1                 | 24              | 1000       | 10                   | 60       | 1.2              | 10               |

$\begin{array}{l} \textbf{note 1}: Square \ pulse, \ lpp = 15A, \ tp=2.5 \mu s.\\ \textbf{note 2}: \ \Delta \ VBR = \alpha T^* \ (Tamb \ -25^\circ C) \ ^* \ VBR \ (25^\circ C) \end{array}$

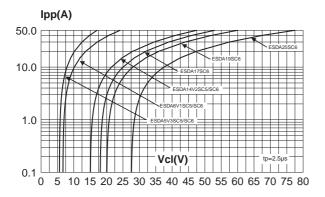

### CALCULATION OF THE CLAMPING VOLTAGE **USE OF THE DYNAMIC RESISTANCE**

The ESDA family has been designed to clamp fast spikes like ESD. Generally the PCB designers need to calculate easily the clamping voltage V<sub>CL</sub>. This is why we give the dynamic resistance in addition to the classical parameters. The voltage across the protection cell can be calculated with the following formula:

VCL = VBR + Rd IPP

Where Ipp is the peak current through the ESDA cell.

### DYNAMIC RESISTANCE MEASUREMENT

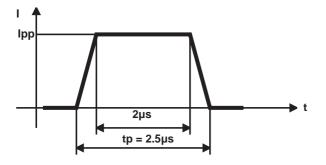

The short duration of the ESD has led us to prefer a more adapted test wave, as below defined, to the classical 8/20µs and 10/1000µs surges.

2.5µs duration measurement wave.

As the value of the dynamic resistance remains stable for a surge duration lower than 20µs, the 2.5µs rectangular surge is well adapted. In addition both rise and fall times are optimized to avoid any parasitic phenomenon during the measurement of Rd.

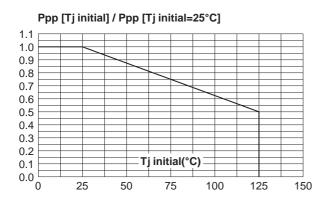

**Fig. 1:** Peak power dissipation versus initial junction temperature.

**Fig. 3:** Clamping voltage versus peak pulse current (Tj initial = 25 °C). Rectangular waveform (tp =  $2.5 \mu$ s).

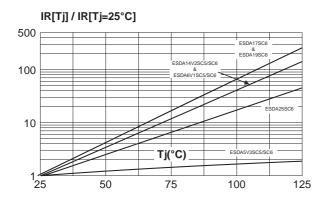

**Fig. 5:** Relative variation of leakage current versus junction temperature (typical values).

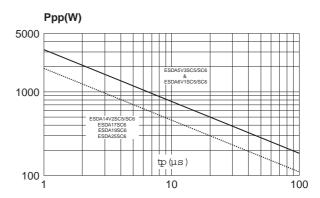

**Fig. 2:** Peak pulse power versus exponential pulse duration (Tj initial = 25 °C).

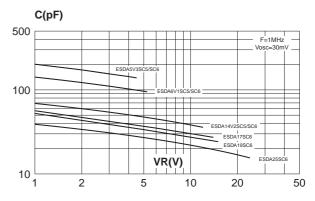

Fig. 4: Capacitance versus reverse applied voltage (typical values).

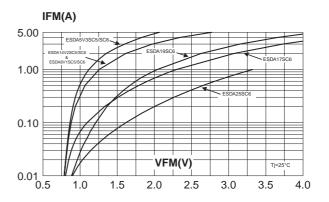

**Fig. 6:** Peak forward voltage drop versus peak forward current (typical values).

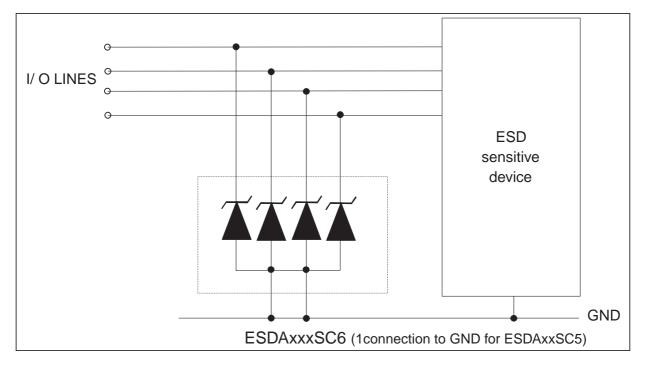

### ESD protection by ESDAXXXSCX

Electrostatic discharge (ESD) is a major cause of failure in electronic systems.

Transient Voltage Suppressors (TVS) are an ideal choice for ESD protection. They are capable of clamping the incoming transient overvoltage to a low enough level such that damage to the protected semiconductor is prevented.

Surface mount TVS arrays offer the best choice for minimal lead inductance.

They serve as parallel protection elements, connected between the signal line and ground. As the transient rises above the operating voltage of the device, the TVS array becomes a low impedance path diverting the transient current to ground.

The ESDAxxSCx array is the ideal board level protection of ESD sensitive semiconductor components.

The tiny SOT23-5L and SOT23-6L packages allow design flexibility in the high density boards where the space saving is at a premium. This enables to shorten the routing and contributes to hardening against ESD.

# ADVICE FOR OPTIMIZING CIRCUIT BOARD LAYOUT

Circuit board layout is a critical design step in the suppression of ESD induced transients. The following guidelines are recommended :

- The ESDAxxSC5/6 should be placed as close as possible to the input terminals or connectors.

- The path length between the ESD suppressor and the protected line should be minimized

- All conductive loops, including power and ground loops should be minimized

- The ESD transient return path to ground should be kept as short as possible.

- Ground planes should be used whenever possible.

### ADVICE FOR OPTIMIZING CIRCUIT BOARD LAYOUT

Circuit board layout is a critical design step in the suppression of ESD induced transients. The following guidelines are recommended:

- The ESDA19SC6 should be placed as close as possible to the input terminals or connectors.

- The path length between the ESD suppressor and the protected line should be minimized.

- All conductive loops, including power and ground loops should be minimized.

- The ESD transient return path to ground should be kept as short as possible.

- Ground planes should be used whenever possible.

### **TECHNICAL INFORMATION**

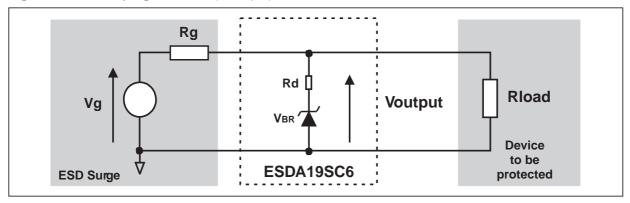

### **ESD PROTECTION**

The **ESDA19SC6** is particularly optimized to perform ESD protection. ESD protection is achieved by clamping the unwanted overvoltage. The clamping voltage is given by the following formula :

$$V_{CL} = V_{BR} + R_d \cdot I_{PP}$$

As shown in figure A1, the ESD strikes are clamped by the transient voltage suppressor.

Fig. A1: ESD clamping behavior (example)

To have a good approximation of the remaining voltages at both VI/O side, we provide the typical dynamical resistance value Rd. By taking into account the following hypothesis :

Rg > Rd and Rload > Rd

we have:

$$VOutput = V_{BR} + R_d \times \frac{V_g}{R_g}$$

The results of the calculation done for Vg = 8 kV, Rg = 330  $\Omega$  (IEC61000-4-2 standard), Vbr = 19 V (typ.) and Rd = 0.80  $\Omega$  (typ.) give:

This confirms the very low remaining voltage across the device to be protected. It is also important to note that in this approximation the parasitic inductance effect was not taken into account. This could be a few tenths of volts during a few nanoseconds at the output side.

47/

6/9

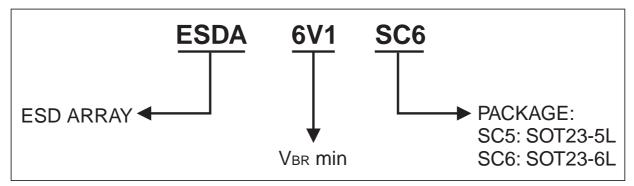

### **ORDER CODE**

### **ORDERING INFORMATION**

| Odering Type | Marking | Package  | Weight  | Base qty | Delivery mode |

|--------------|---------|----------|---------|----------|---------------|

| ESDA5V3SC5   | EC53    | SOT23-5L | 16.7 mg | 3000     | Tape & reel   |

| ESDA5V3SC6   | ES53    | SOT23-6L | 16.7 mg | 3000     | Tape & reel   |

| ESDA6V1SC5   | EC61    | SOT23-5L | 16.7 mg | 3000     | Tape & reel   |

| ESDA6V1SC6   | ES61    | SOT23-6L | 16.7 mg | 3000     | Tape & reel   |

| ESDA14V2SC5  | EC15    | SOT23-5L | 16.7 mg | 3000     | Tape & reel   |

| ESDA14V2SC6  | ES15    | SOT23-6L | 16.7 mg | 3000     | Tape & reel   |

| ESDA17SC6    | ES17    | SOT23-6L | 16.7 mg | 3000     | Tape & reel   |

| ESDA19SC6    | ES19    | SOT23-6L | 16.7 mg | 3000     | Tape & reel   |

| ESDA25SC6    | ES25    | SOT23-6L | 16.7 mg | 3000     | Tape & reel   |

Epoxy meets UL94-V0 standard

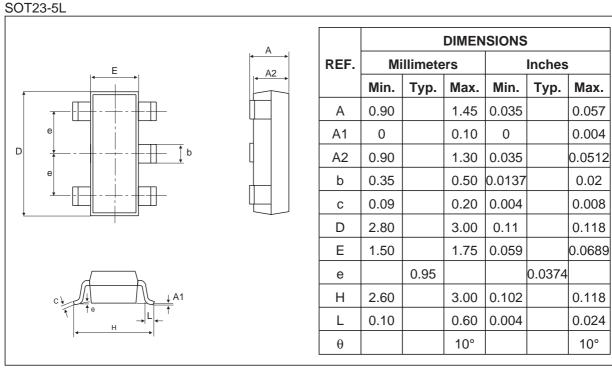

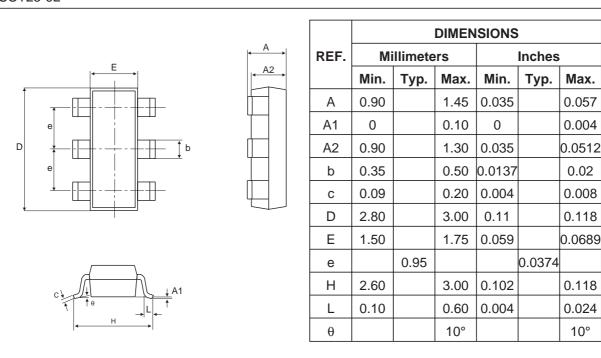

### PACKAGE MECHANICAL DATA

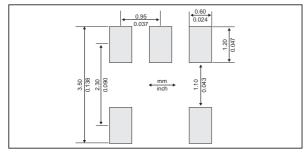

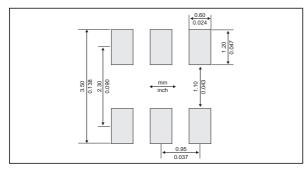

### FOOT PRINT

#### PACKAGE MECHANICAL DATA SOT23-6L

### FOOT PRINT

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2002 STMicroelectronics - Printed in Italy - All rights reserved.

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore Spain - Sweden - Switzerland - United Kingdom - United States.

http://www.st.com

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.